# IMPROVING POWER of L1 DATA CACHE and REGISTER FILE UTILIZING CRITICAL PATH INSTRUCTIONS

A Thesis

prepared by

Kuang-Lun Chen

in the

Department of Electrical Engineering

Lakehead University

Thunder Bay, Ontario, Canada December, 2013

#### **Abstract**

As transistor's feature size shrinks, power becomes one of the limiting factors in design of modern processors. Cache and register file are the two power hungry components in processors, consuming more than one third of total processors' power budget. In this thesis, we propose new architectures for cache and register file to reduce power consumption. In the new architectures, we have SRAM cells operating at two different voltage levels and we change the structure of the cells so that they dynamically switch between nominal and reduced supply voltage.

Since power is proportional to voltage squared, an effective method to reduce power is lowering supply voltage. However, one of the side effects of using SRAM cells with reduced voltage is performance penalty. As supply voltage reduces, it takes longer to read/write from/to an SRAM cell. In this thesis, we exploit critical path instructions to overcome the performance impact of voltage scaling. Critical path instructions are chain of dependent instructions that constrain speed of processors. Those cells that are accessed frequently by critical instructions are assigned to use nominal supply voltage to preserve performance. On the other side, the cells that are seldom accessed by critical instructions are assigned to low supply voltage to reduce power consumption. To reduce overhead of voltage switching, we monitor critical instructions within long intervals and adjust the voltage of cells only when the intervals are elapsed.

We have evaluated our optimization techniques using a combination of circuit and architectural simulators. First, we used HSPICE to measure both dynamic and static power and also latency of SRAM cells for nominal and reduced supply voltages. Then, the results from HSPICE were fed into Simplescalar for architectural evaluations. Our simulation results reveal that the low power cache and register file reduce power consumption significantly with negligible impact on performance.

# **Acknowledgements**

I thank my supervisors at Lakehead University, Dr Ehsan Atoofian and Dr Ali Manzak. It's their common interest spawned the idea and the topic of this research. Especial thanks to Dr Ehsan Atoofian for his financial support coming in time of need and also for his valuable advises on Simplescalar simulations.

I also would like to thank my parents, Pin-Ching Chen and Shiow-Min Yang who have been given me encouragements since I was a child. Thanks go to my sister Ellen Chen too who walked me through various difficult times.

# **Table of Contents**

| Abstract                                                                           | ii   |

|------------------------------------------------------------------------------------|------|

| Acknowledgements                                                                   | iii  |

| Table of Contents                                                                  | iv   |

| List of Figures                                                                    | viii |

| List of Tables                                                                     | xii  |

| Section 1 Introduction                                                             | 1    |

| 1.1 Motivation and outline of study                                                | 1    |

| 1.2 Thesis Overview                                                                | 3    |

| Section 2 Literature Review                                                        | 4    |

| Section 3 Super-scalar Processor Architecture                                      | 21   |

| 3.1 Introduction                                                                   | 21   |

| 3.2 Instruction fetch.                                                             | 24   |

| 3.3 Instruction decode, rename and dispatch                                        | 25   |

| 3.4 Instruction issue and parallel execution.                                      | 29   |

| 3.5 Memory and cache                                                               | 30   |

| 3.5.1 Memory gap                                                                   | 30   |

| 3.5.2 Direct-mapped cache                                                          | 32   |

| 3.5.3 Set-associative cache                                                        | 33   |

| 3.6 Commit                                                                         | 34   |

| Section 4 Low Power Cache, Low Power Register File, and Critical Path Instructions | 35   |

| 4.1 SRAM basics                                                                    | 35   |

| 4.1.1 Standard 6T SRAM cells                                                       | 35   |

| 4.1.2 4T2R topology SRAM cells                                                     | 36   |

| 4.1.3 Read operation                                                               | 37   |

| 4.1.4 Write operation                                                              | 40   |

| 4.1.5 Transistor sizing constraints                                                | 41   |

| 4.1.6 SRAM columns                                                                 | 43   |

| 4.1.6.1 Pre-charge                                                                 | 44   |

| 4.1.6.2 Column decoder                                                             | 45   |

| 4.1.6.3 Write driver                                                               | 47   |

| 4.1.6.4 Sense amplifier                                                            | 48   |

| 4.1.6.5 Latch                                          | 52 |

|--------------------------------------------------------|----|

| 4.1.6.6 Level shifter                                  | 53 |

| 4.1.6.7 Row decoder                                    | 55 |

| 4.1.6.8 Tag comparison                                 | 56 |

| 4.2 Low power cache                                    | 57 |

| 4.3 Low power register file                            | 59 |

| 4.4 Critical path instruction prediction               | 60 |

| Section 5 Methodology and Results                      | 64 |

| 5.1 Low power cache                                    | 64 |

| 5.1.1 Critical instruction policy (QOLD)               | 64 |

| 5.1.2 HSPICE simulations and results                   | 65 |

| 5.1.2.1 Decoder                                        | 65 |

| 5.1.2.2 SRAM column                                    | 69 |

| 5.1.2.3 Tag Comparison                                 | 77 |

| 5.1.2.4 Summary                                        | 80 |

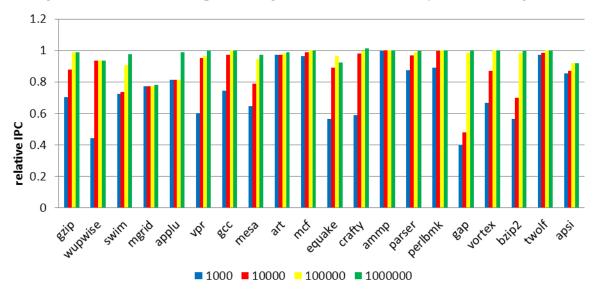

| 5.1.3 SP2K benchmark results (QOLD)                    | 81 |

| 5.1.3.1 Methodology                                    | 81 |

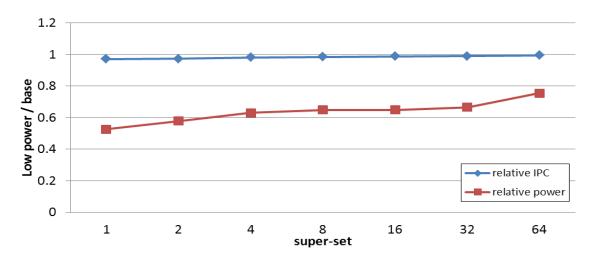

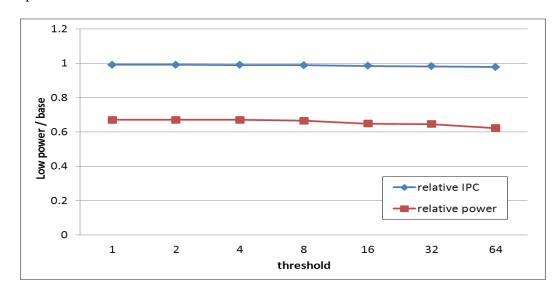

| 5.1.3.2 Impact of super-set size and counter threshold | 82 |

| 5.1.3.3 Impact of criticality interval (M)             | 84 |

| 5.1.3.4 Impact of N                                    | 85 |

| 5.1.3.5 Summary                                        | 86 |

| 5.2 Low power register file                            | 87 |

| 5.2.1 Critical instruction policy (QOLD)               | 87 |

| 5.2.2 HSPICE simulations and results                   | 88 |

| 5.2.2.1 Decoder                                        | 88 |

| 5.2.2.2 SRAM column                                    | 89 |

| 5.2.2.3 Summary                                        | 89 |

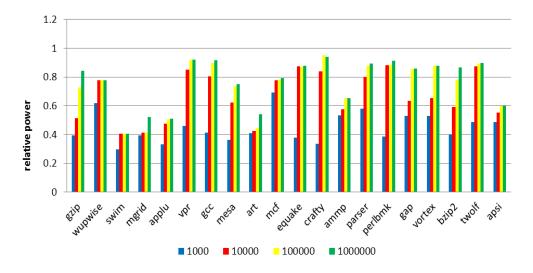

| 5.2.3 SP2K benchmark results (QOLD)                    | 90 |

| 5.2.3.1 Methodology                                    | 90 |

| 5.2.3.2 Impact of super-set size and counter threshold | 90 |

| 5.2.3.3 Impact of criticality interval (M)             | 92 |

| 5.2.3.4 Impact of N                                    | 93 |

| 5.2.3.5 Summary                                          | 94  |

|----------------------------------------------------------|-----|

| Section 6 Conclusions and future work                    | 95  |

| Section 7 APPENDIX                                       | 97  |

| 7.1 Methodology and Results (QCONS)                      | 97  |

| 7.1.1 Low Power Cache                                    | 97  |

| 7.1.1.1 Methodology                                      | 97  |

| 7.1.1.2 Impact of super-set size and counter threshold   | 97  |

| 7.1.1.3 Impact of criticality interval (M)               | 99  |

| 7.1.1.4 Impact of C                                      | 100 |

| 7.1.1.5 Distribution of number of dependent instructions | 101 |

| 7.1.1.6 Summary                                          | 102 |

| 7.1.2 Low Power Register Files                           | 102 |

| 7.1.2.1 Methodology                                      | 102 |

| 7.1.2.2 Impact of super-set size and counter threshold   | 102 |

| 7.1.2.3 Impact of criticality interval (M)               | 104 |

| 7.1.2.4 Impact of C                                      | 105 |

| 7.1.2.5 Distribution of number of dependent instructions | 106 |

| 7.1.2.6 Summary                                          | 108 |

| 7.2 Methodology and Results (FREED)                      | 108 |

| 7.2.1 Low Power Cache                                    | 108 |

| 7.2.1.1 Methodology                                      | 108 |

| 7.2.1.2 Impact of super-set size and counter threshold   | 108 |

| 7.2.1.3 Impact of criticality interval (M)               | 110 |

| 7.2.1.4 Impact of F                                      | 111 |

| 7.2.1.5 Distribution of number of dependent instructions | 112 |

| 7.2.1.6 Summary                                          | 113 |

| 7.2.2 Low Power Register Files                           | 113 |

| 7.2.2.1 Methodology                                      | 113 |

| 7.2.2.2 Impact of super-set size and counter threshold   | 113 |

| 7.2.2.3 Impact of criticality interval (M)               | 115 |

| 7.2.2.4 Impact of F                                      | 116 |

| 7.2.2.5 Distribution of number of dependent instructions | 117 |

| 7.2.2.6 Summary | 119 |

|-----------------|-----|

| References      | 120 |

# **List of Figures**

| Figure 2-1: Example loop                                                                  | 5  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2-2: (a) A schedule for architecture a1 (b) A schedule for architecture a2         | 5  |

| Figure 2-3: Access and timing for design options                                          | 9  |

| Figure 2-4: Anatomy of a Dynamically Resizable instruction cache (DRI i-cache)            | 10 |

| Figure 2-5: MTCMOS SRAM cell schematics                                                   | 13 |

| Figure 2-6: Traditional cache vs filter cache                                             | 14 |

| Figure 2-7: Structure of a sub-banking cache                                              | 15 |

| Figure 2-8: MIPS pipeline processor                                                       | 16 |

| Figure 2-9: A drowsy register file cell                                                   | 18 |

| Figure 2-10: A gated ground register file cell                                            | 20 |

| Figure 3-1: (a) An example of sequential execution. (b) An example of pipelined execution | 22 |

| Figure 3-2: A conceptual execution flow of a superscalar processor                        | 23 |

| Figure 3-3: Organization of a superscalar processor                                       | 24 |

| Figure 3-4: An example of data hazard                                                     | 26 |

| Figure 3-5: Register renaming.                                                            | 27 |

| Figure 3-6: Physical register reclamation                                                 | 28 |

| Figure 3-7: Renaming in re-order buffer                                                   | 29 |

| Figure 3-8: A typical reservation station                                                 | 30 |

| Figure 3-9: A multiple reservation station queue                                          | 30 |

| Figure 3-10: Memory gap                                                                   | 31 |

| Figure 3-11: A 2k byte, 32 bit address, direct-mapped cache                               | 32 |

| Figure 3-12: A 2-way set-associative cache                                                | 34 |

| Figure 4-1: An SRAM cell                                                                  | 36 |

| Figure 4-2: A 4T2R SRAM cell.                                                             | 36 |

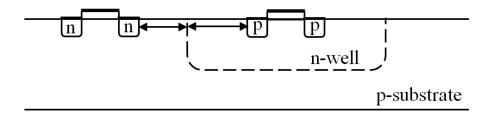

| Figure 4-3: A profile of an NMOS and PMOS in silicon.                                     | 37 |

| Figure 4-4: An SRAM cell in read operation                                                | 38 |

| Figure 4-5: An SRAM cell for write operation                                              | 40 |

| Figure 4-6: SRAM sizing constraints                                                       | 42 |

| Figure 4-7: Final SRAM cell in our design.                                                | 43 |

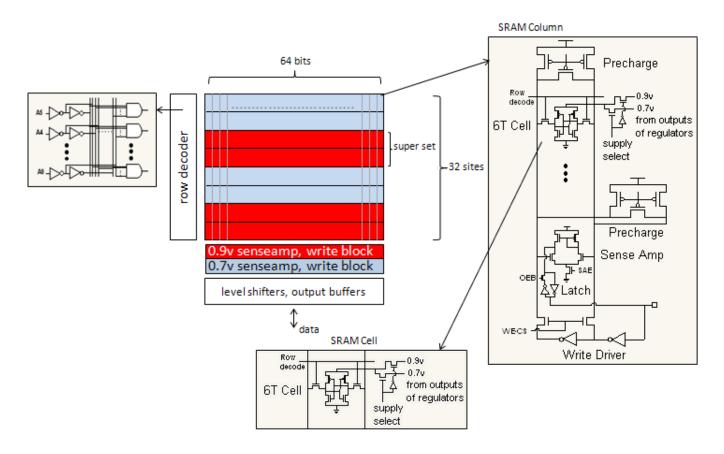

| Figure 4-8: A typical SRAM column structure.                                              | 44 |

| Figure 4-9: Circuit of pre-charge.                                                        | 45 |

| Figure 4-10: SRAM columns sharing same analog resources.                                             | 46    |

|------------------------------------------------------------------------------------------------------|-------|

| Figure 4-11: Column decoder (CD).                                                                    | 47    |

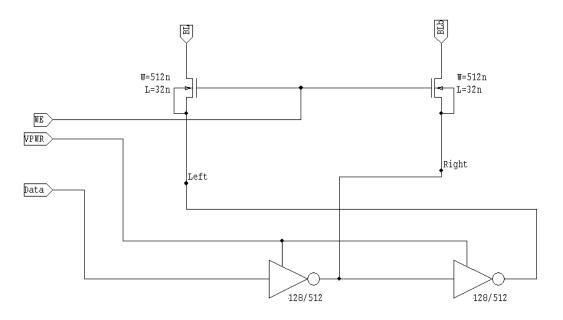

| Figure 4-12: Write driver                                                                            | 48    |

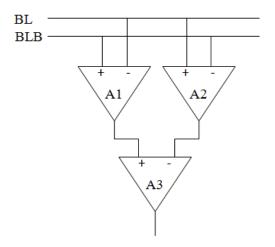

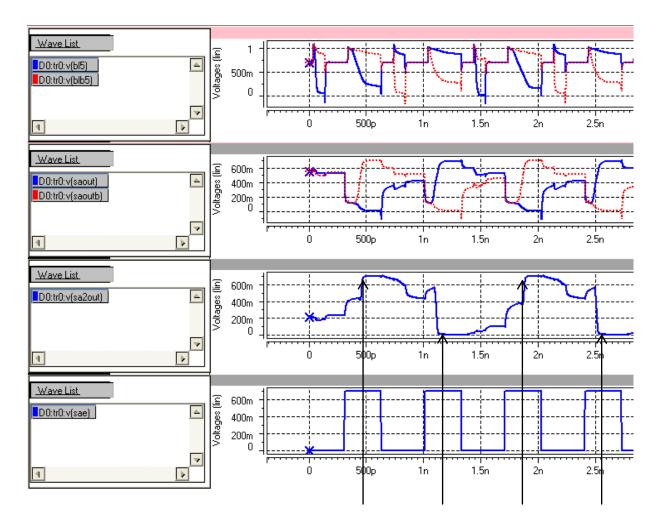

| Figure 4-13: 2-level sense amplifier.                                                                | 49    |

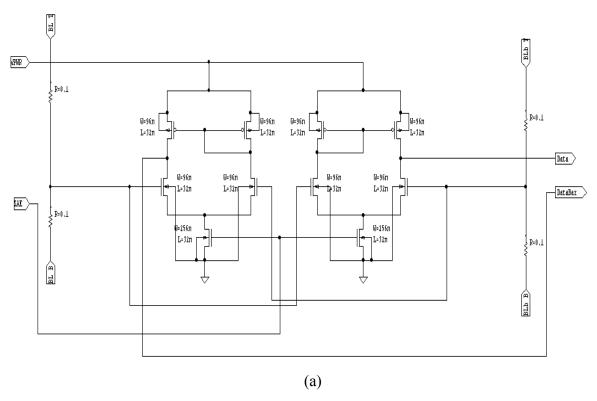

| Figure 4-14: (a) First stage (b) Final stage of sense amplifier.                                     | 50    |

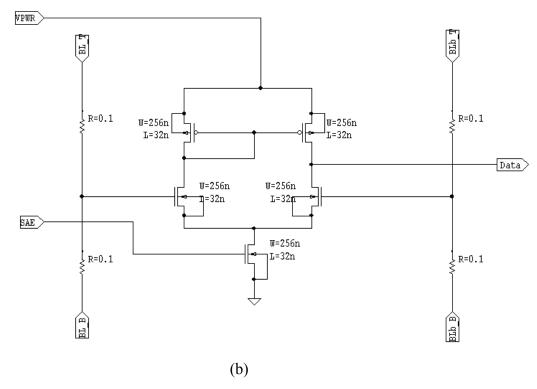

| Figure 4-15: Waveforms of sense amplifier block.                                                     | 51    |

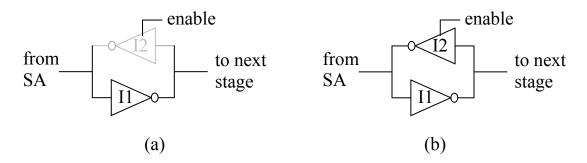

| Figure 4-16: Latch states when (a) SAE is de-asserted (b) SAE is asserted.                           | 52    |

| Figure 4-17: Schematic of gated data latch.                                                          | 53    |

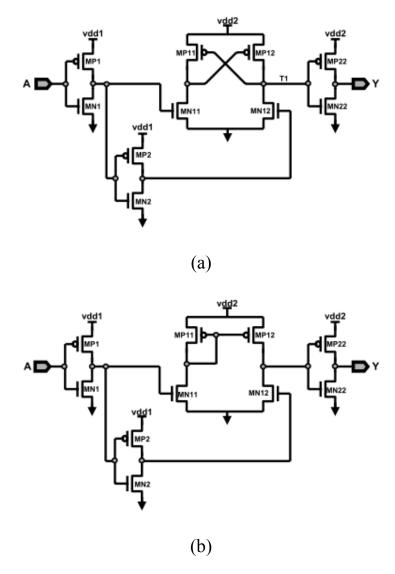

| Figure 4-18: Conventional level shifters (a) latch-type (b) current-mirror type                      | 54    |

| Figure 4-19: Schematic of our design.                                                                | 55    |

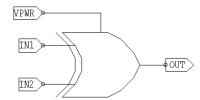

| Figure 4-20: Pull down network of a two input NAND gate.                                             | 56    |

| Figure 4-21: Truth table of XOR gate and its symbol.                                                 | 57    |

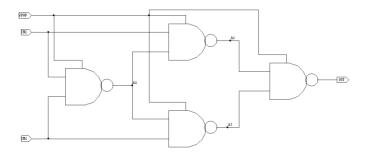

| Figure 4-22: Schematic of XOR implementation.                                                        | 57    |

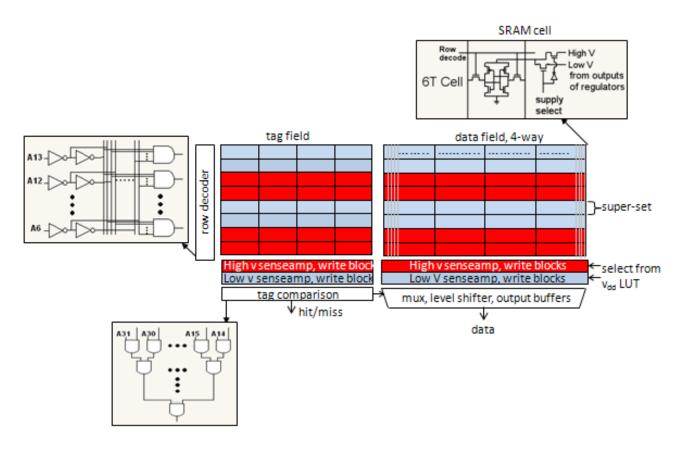

| Figure 4-23: Low power cache design.                                                                 | 59    |

| Figure 4-24: Low power register file.                                                                | 60    |

| Figure 4-25: A code fragment of showing data dependence.                                             | 61    |

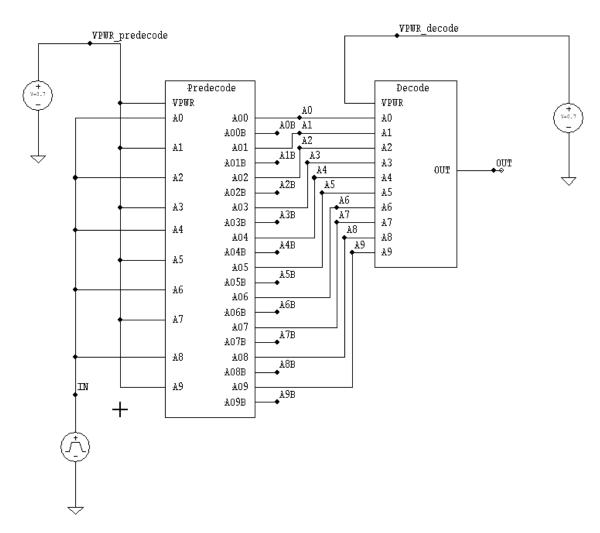

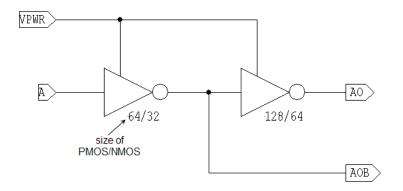

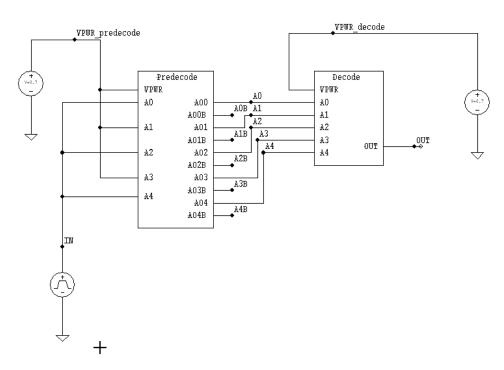

| Figure 5-1: Decoder simulation setup.                                                                | 66    |

| Figure 5-2: Predecoder circuit for each input.                                                       | 67    |

| Figure 5-3: Row decoder circuit for each row.                                                        | 67    |

| Figure 5-4: Waveforms for decoder (a) 0.7v (b) 0.9v.                                                 | 69    |

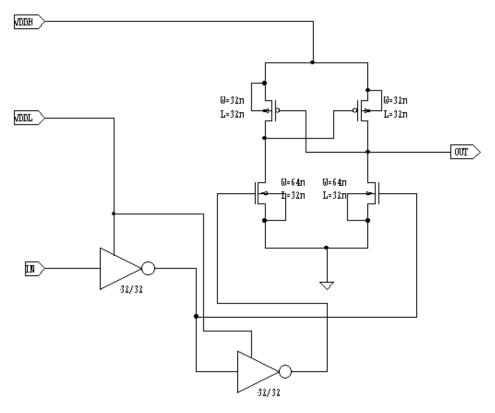

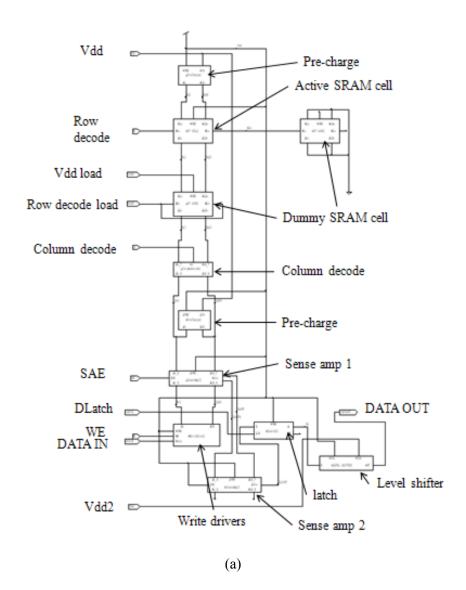

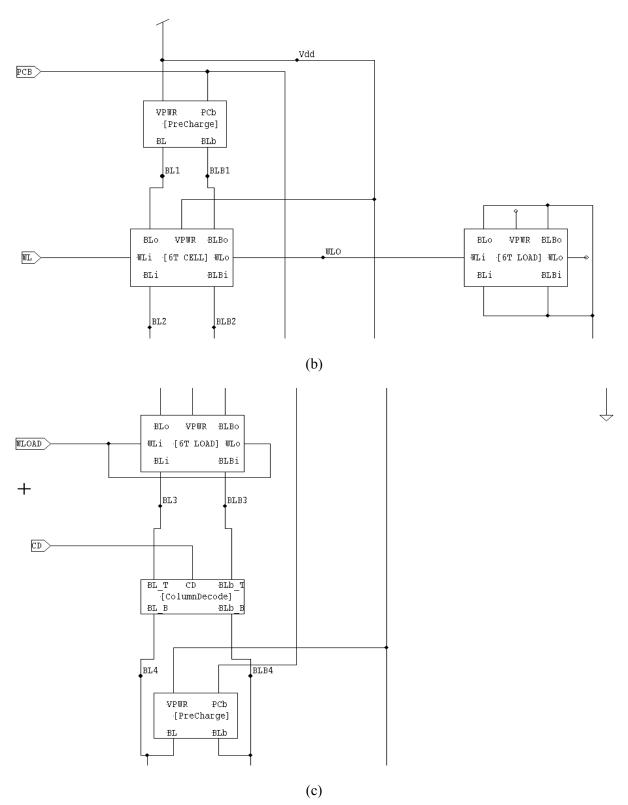

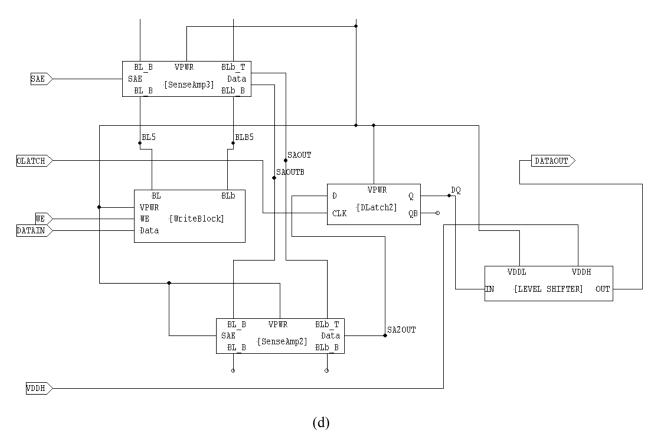

| Figure 5-5: (a) Structure of an SRAM column (b) details of top section (c) details of middle section | n     |

| (d) details of bottom section.                                                                       | 72    |

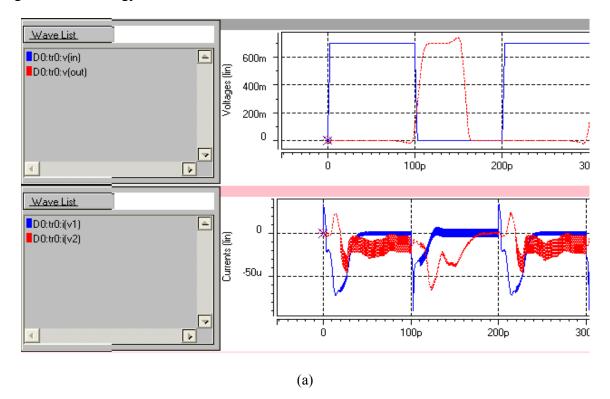

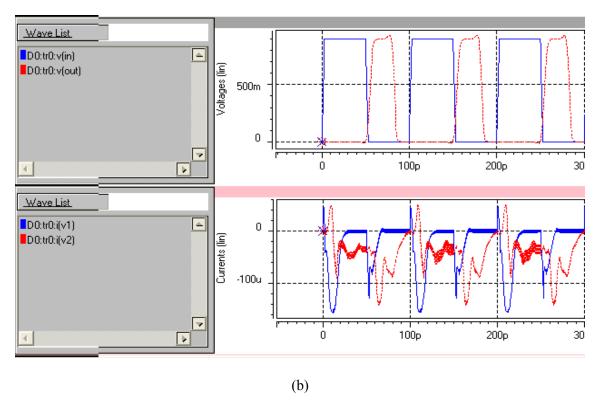

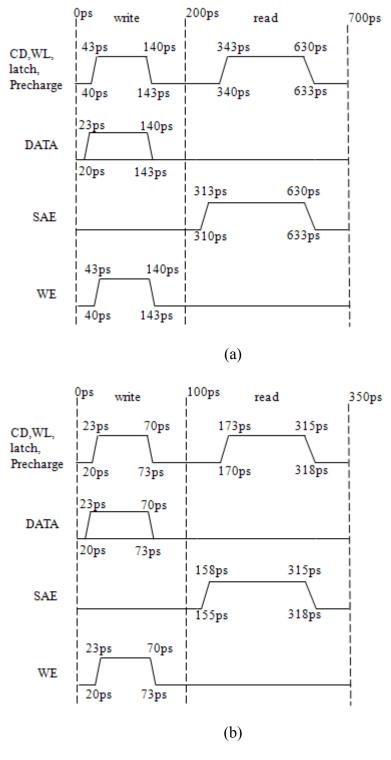

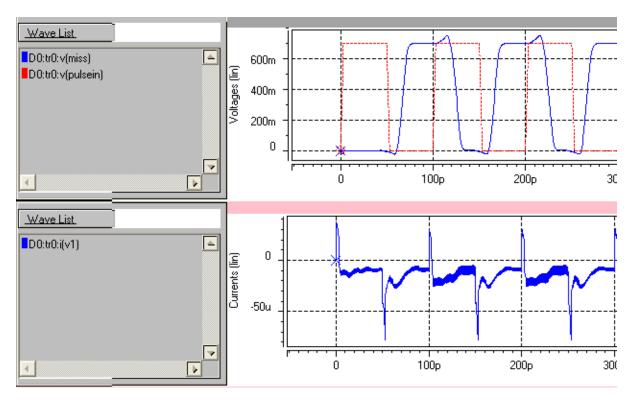

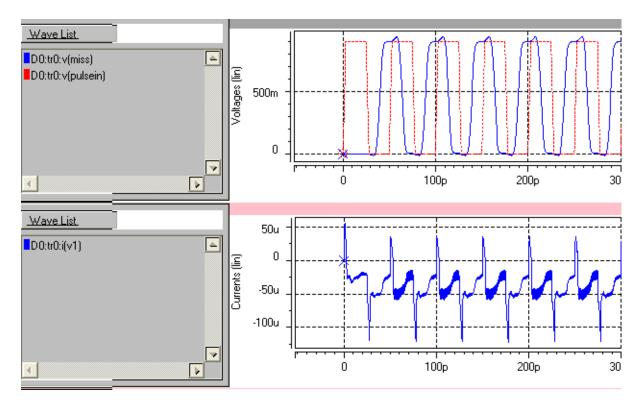

| Figure 5-6: (a) 0.7v time set (b) 0.9v time set                                                      | 73    |

| Figure 5-7: 0.7v SRAM column simulation waveforms.                                                   | 75    |

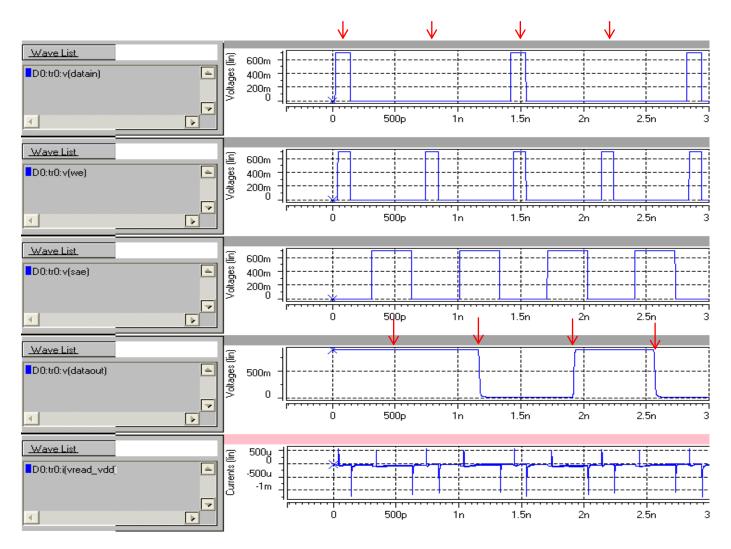

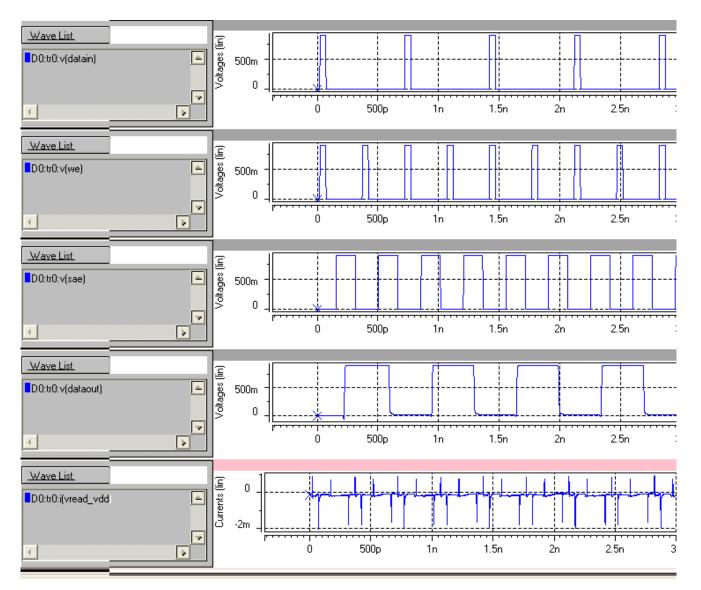

| Figure 5-8: 0.9v SRAM column simulation waveforms.                                                   | 76    |

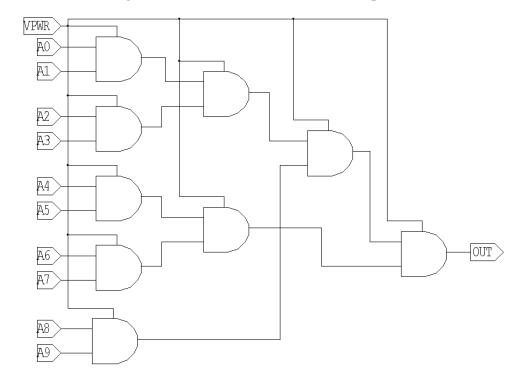

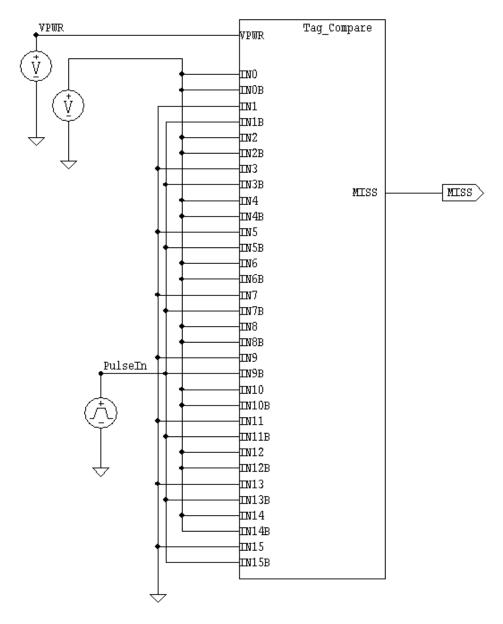

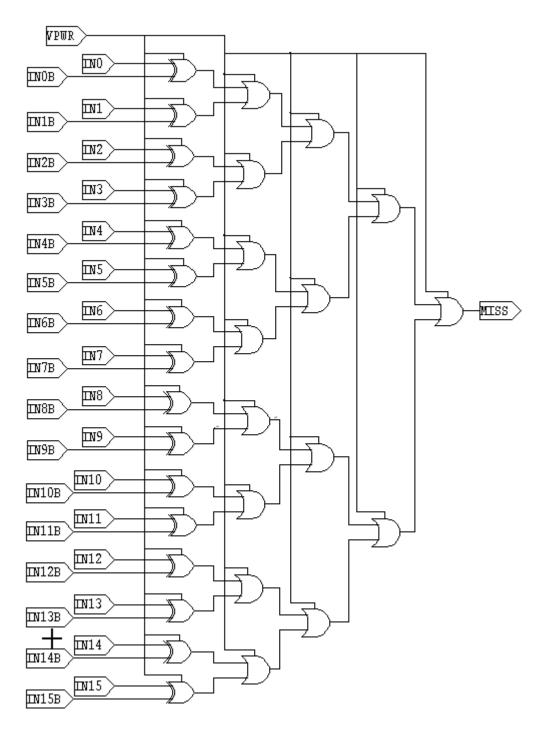

| Figure 5-9: Simulation set up for tag comparison.                                                    | 77    |

| Figure 5-10: Schematic for tag comparison.                                                           | 78    |

| Figure 5-11: 0.7v Simulation waveform for tag comparison.                                            | 79    |

| Figure 5-12: 0.9v simulation waveform for tag comparison.                                            | 80    |

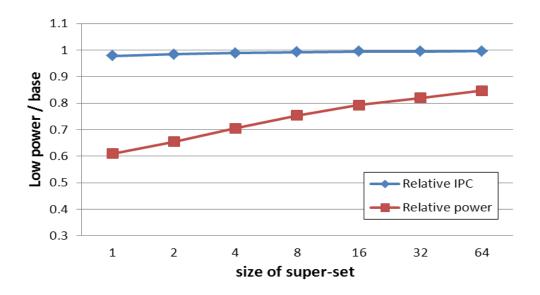

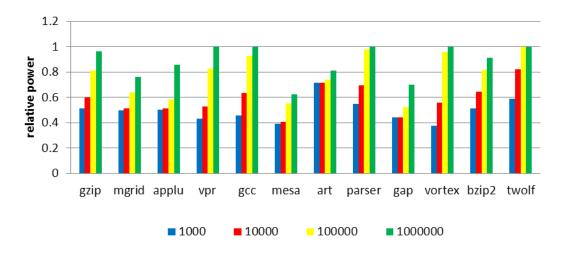

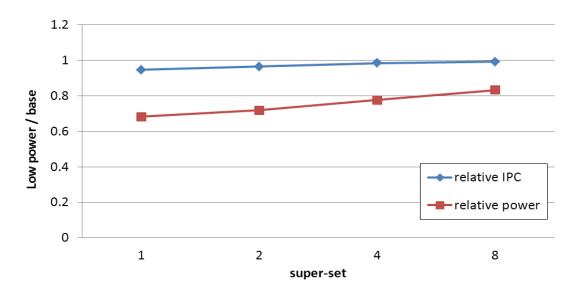

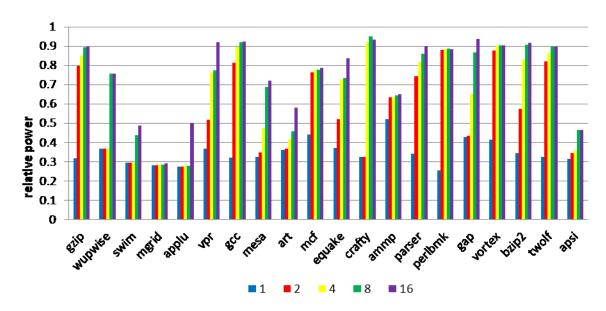

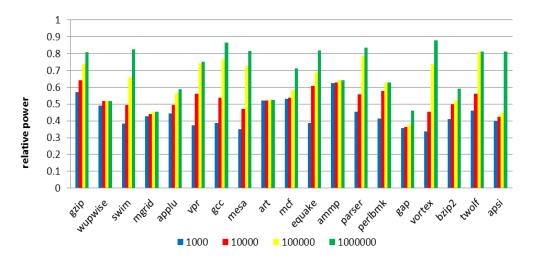

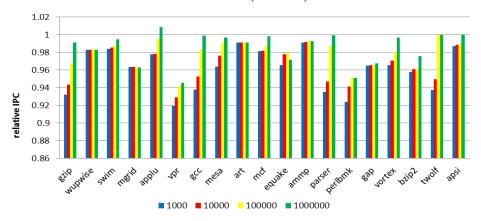

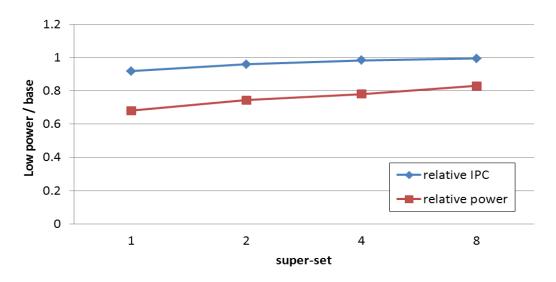

| Figure 5-13: Impact of super-set size in Spec2000 benchmarks (N=8, threshold=8 and M=100000)         | ). 83 |

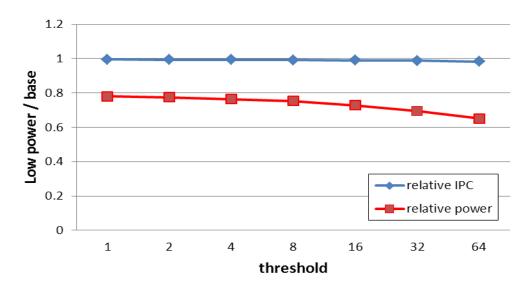

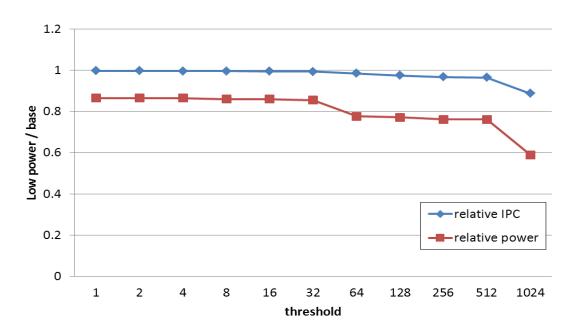

| Figure 5-14: Impact of threshold on Spec2000 benchmarks. (super-set=8 rows, N=8, M=100000) .         | 84    |

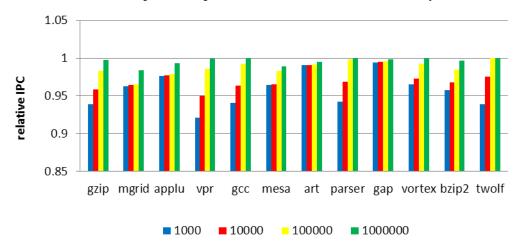

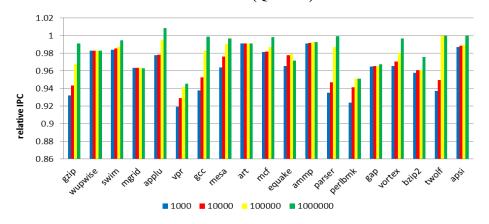

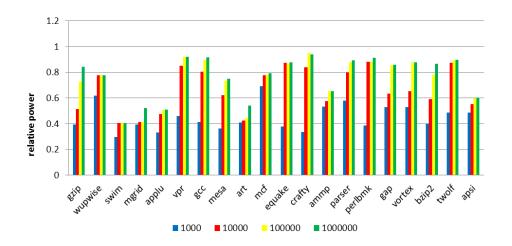

| Figure 5-15: Power consumption in Spec2000 benchmarks when criticality interval changes              | 85    |

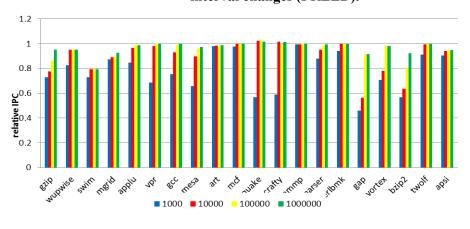

| Figure 5-16: Performance in Spec2000 benchmarks when criticality interval changes.                                                              | 85   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5-17: Power consumption in Spec2000 benchmarks when N increase                                                                           | 86   |

| Figure 5-18: Performance in Spec2000 benchmarks when N increase.                                                                                | 86   |

| Figure 5-19: Simulation schematic for decoder in register file                                                                                  | 88   |

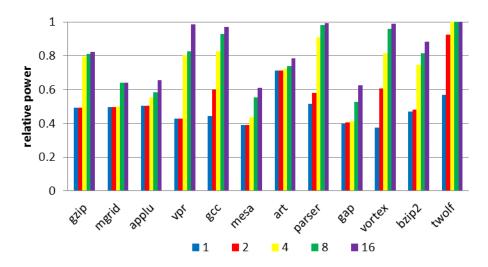

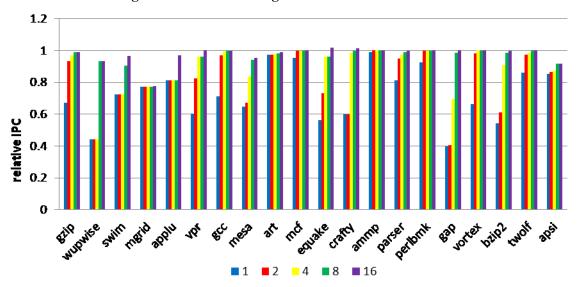

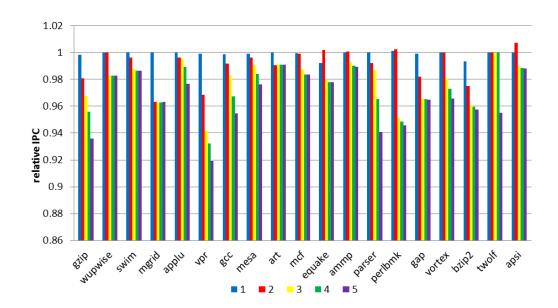

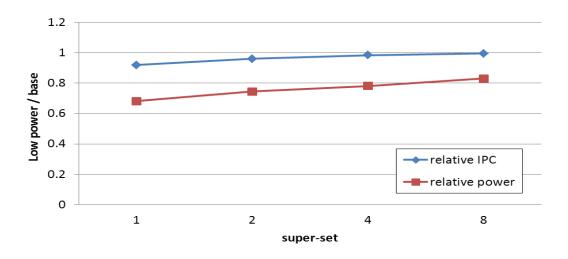

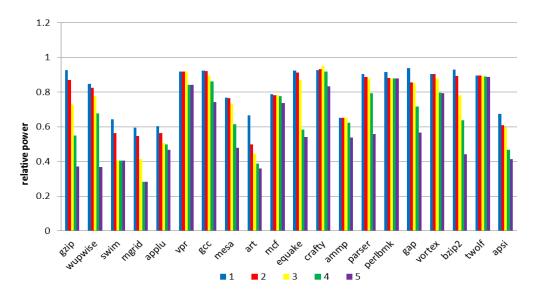

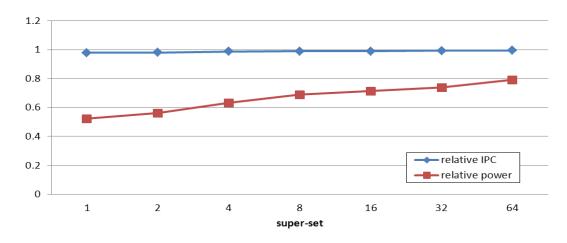

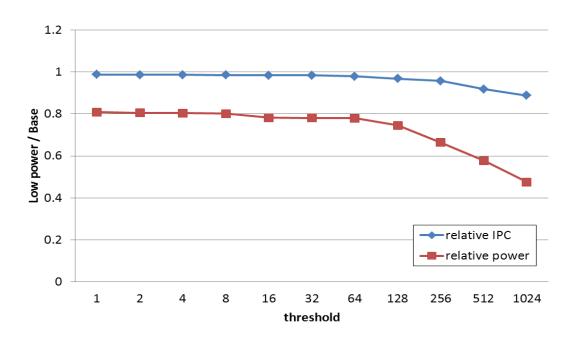

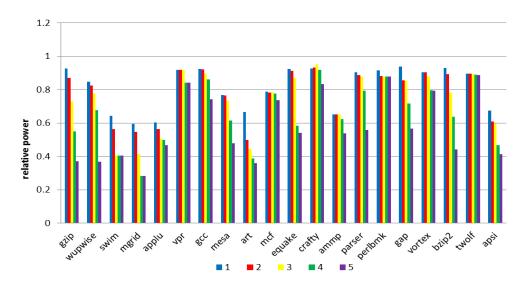

| Figure 5-20: Impact of super-set size on power and performance of register files (N=8, threshold                                                | =64  |

| and M=100000)                                                                                                                                   | 91   |

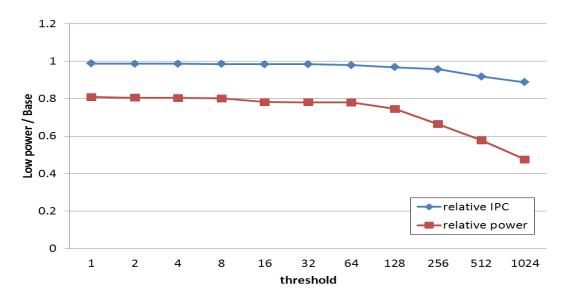

| Figure 5-21: Impact of threshold on power and performance of register files. (super-set=4 rows, 1                                               | N=8, |

| M=100000)                                                                                                                                       | 92   |

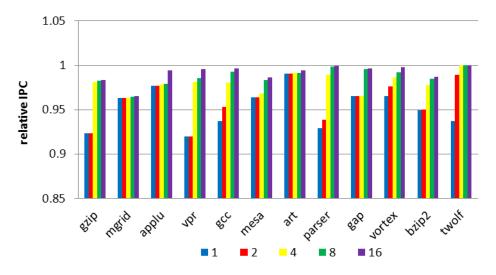

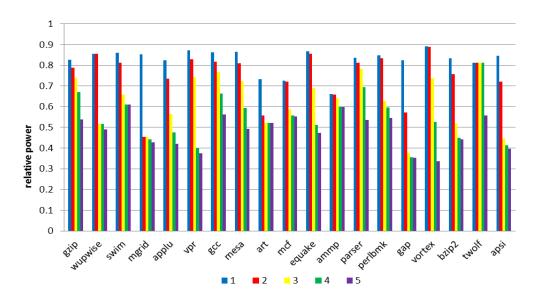

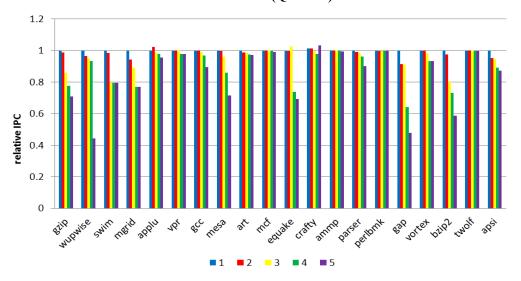

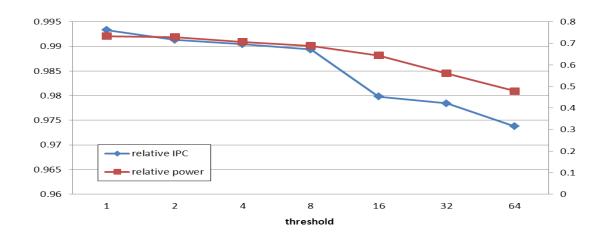

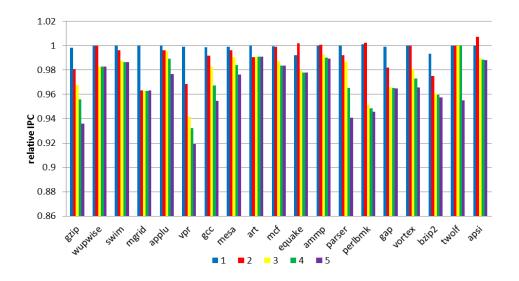

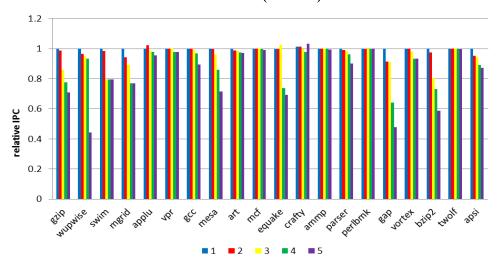

| Figure 5-22: Power consumption in register files when criticality interval changes                                                              | 93   |

| Figure 5-23: Performance in register files when criticality interval changes.                                                                   | 93   |

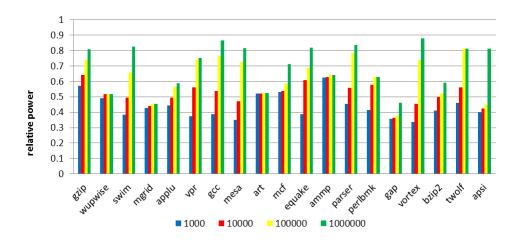

| Figure 5-24: Power of register files when N increase.                                                                                           | 94   |

| Figure 5-25: Performance of register files when N increase.                                                                                     | 94   |

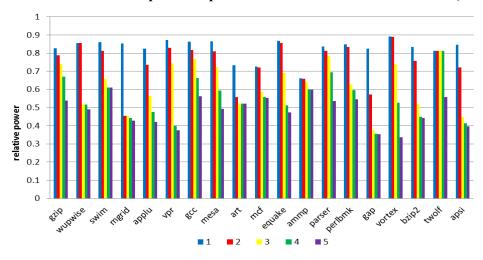

| Figure 7-1: Impact of super-set size in Spec2000 benchmarks (QCONS) (C=3, threshold=16 and M=100000).                                           |      |

| Figure 7-2: Impact of threshold on Spec2000 benchmarks (QCONS) (super-set=8 rows, C=3, M=100000).                                               |      |

| Figure 7-3: Power consumption in Spec2000 benchmarks when criticality interval changes (QCC                                                     |      |

| Figure 7-4: Performance in Spec2000 benchmarks when criticality interval changes (QCONS)                                                        | 99   |

| Figure 7-5: Power consumption in Spec2000 benchmarks when C increases (QCONS)                                                                   | 100  |

| Figure 7-6: Performance in Spec2000 benchmarks when C increases (QCONS)                                                                         | 101  |

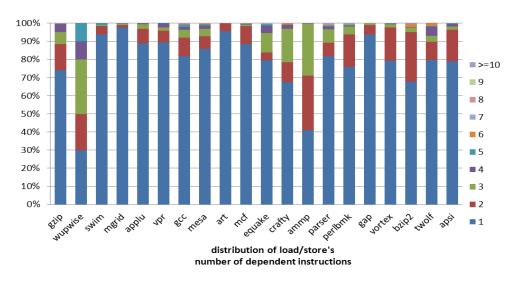

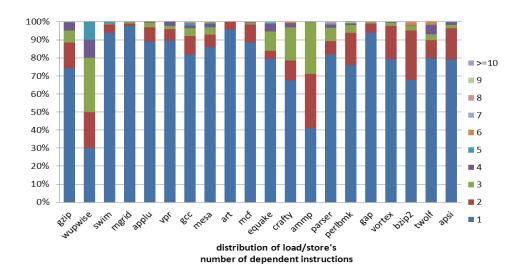

| Figure 7-7: Distribution of load/store's number of dependent instructions (QCONS)                                                               |      |

| threshold=16 and M=100000).  Figure 7-9: Impact of threshold on power and performance of register files (QCONS) (super-set=rows, C=3, M=100000) | =8   |

| Figure 7-10: Power consumption of register files in Spec2000 benchmarks when criticality intervention changes (QCONS).                          |      |

| Figure 7-11: Performance of register files in Spec2000 benchmarks when criticality interval chan (QCONS).                                       | _    |

| Figure 7-12: Power consumption of register files in Spec2000 benchmarks when C increases (QCONS).                                               | 106  |

| Figure 7-13: Performance of register files in Spec2000 benchmarks when C increases (QCONS) 106      |

|-----------------------------------------------------------------------------------------------------|

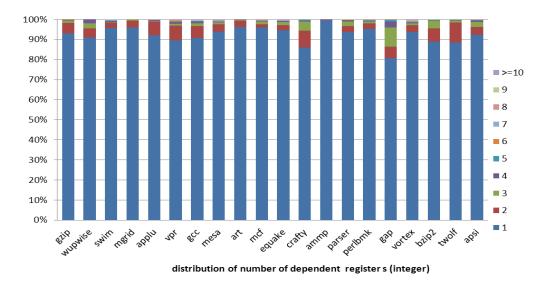

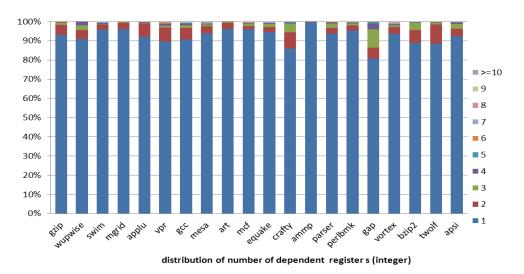

| Figure 7-14: Distribution of number of dependent integer registers                                  |

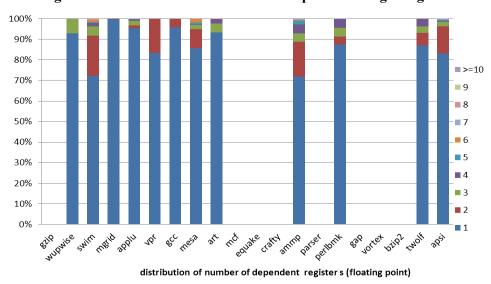

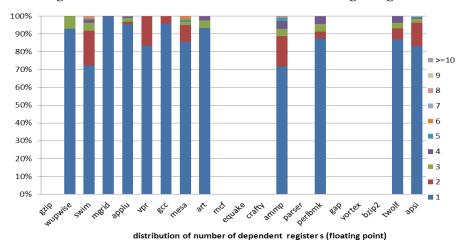

| Figure 7-15: Distribution of number of dependent floating point registers                           |

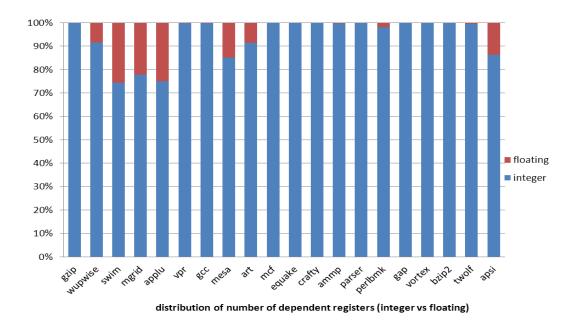

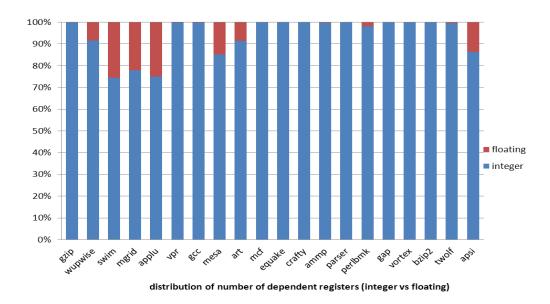

| Figure 7-16: Distribution of dependent registers (integer vs floating point)                        |

| Figure 7-17: Impact of super-set size in Spec2000 benchmarks (FREED) (F=2, threshold=8 and          |

| M=10000)                                                                                            |

| Figure 7-18: Impact of threshold on Spec2000 benchmarks (FREED) (super-set=8 rows, F=2,             |

| M=10000)110                                                                                         |

| Figure 7-19: Power consumption in Spec2000 benchmarks when criticality interval changes             |

| (FREED)111                                                                                          |

| Figure 7-20: Performance in Spec2000 benchmarks when criticality interval changes (FREED) 111       |

| Figure 7-21: Power consumption in Spec2000 benchmarks when F increases (FREED)112                   |

| Figure 7-22: Performance in Spec2000 benchmarks when F increases (FREED)                            |

| Figure 7-23: Distribution of load/store's number of dependent instructions (FREED)                  |

| Figure 7-24: Impact of super-set size on power and performance of register files (FREED) (F=2,      |

| threshold=16 and M=10000)                                                                           |

| Figure 7-25: Impact of threshold on power and performance of register files (FREED) (super-set=8    |

| rows, F=2, M=10000)115                                                                              |

| Figure 7-26: Power consumption of register files in Spec2000 benchmarks when criticality interval   |

| changes (FREED)                                                                                     |

| Figure 7-27: Performance of register files in Spec2000 benchmarks when criticality interval changes |

| (FREED)                                                                                             |

| Figure 7-28: Power consumption of register files in Spec2000 benchmarks when F increases            |

| (FREED)117                                                                                          |

| Figure 7-29: Performance of register files in Spec2000 benchmarks when F increases (FREED)117       |

| Figure 7-30: Distribution of number of freed integer registers                                      |

| Figure 7-31: Distribution of number of freed floating point registers                               |

| Figure 7-32: Distribution of freed registers (integer vs floating point)                            |

# **List of Tables**

| Table 2-1: Memory Hierarchy, iMac G5                               | 7  |

|--------------------------------------------------------------------|----|

| Table 5-1: Total energy consumption in decoder                     | 69 |

| Table 5-2: Total energy consumptions in SRAM columns               | 76 |

| Table 5-3: Total energy consumptions in tag comparator             | 80 |

| Table 5-4: Summary of total power per cycle and cycle time, 2.8GHz | 81 |

| Table 5-5. Baseline processor configuration                        | 81 |

| Table 5-6: Register file size                                      | 88 |

| Table 5-7: Total energy consumptions in register file decoder.     | 89 |

| Table 5-8: Total energy consumptions in register file SRAM columns | 89 |

| Table 5-9: Summary of register file's total power and cycle time   | 90 |

#### **Section 1 Introduction**

### 1.1 Motivation and outline of study

Semiconductor technology scaling in the recent decades has enabled significant improvement in performance of processors. However, this performance improvement is accompanied by an increase in power consumption of processors [1]. Higher power consumption requires expensive packaging and cooling systems, increasing cost and reducing reliability of computer systems. As such, power consumption became the first-order design constrain in all aspects of computer design.

In contemporary processors, a large fraction of chip area is dedicated to the caches and register files and with each technology generation, this fraction continues to grow. For example, Gowan et al. estimated that caches are the third highest power hungry component in DEC's Alpha 21264 microprocessor, consuming 15% of the total power [2]. S. Park et al. suggested that register files may consume up to 25% of total processor power when running embedded programs [21]. An effective method to reduce power consumption is to lower the power supply voltage. Since power is proportional to supply voltage squared a moderate reduction in voltage leads to significant reduction in power. However, the downside of lower voltage is performance degradation. Therefore, one must be careful on applying voltage scaling so that the impact on performance is minimal.

The motivation of this study is to find a way of balancing performance improvement and power reduction. We exploit critical path information to reduce power of L1 data cache and register file and at the same time reduce performance loss due to reduced supply voltage.

To limit performance degradation of voltage scaling, we use critical path instructions. Critical path instructions are chains of dependent instructions that determine programs' execution time [3]. To boost performance of processors, it is necessary to execute critical path instructions as quickly as possible. On the other side, instructions that can be delayed one or more cycles without affecting programs' completion time are called non-critical instructions. E. Tune *et al.* proposed a number of methods to identify critical path

instructions dynamically [3]. We use oldest instruction method to detect critical instructions as this method is more accurate than the other methods, such as Qcons in which the number of consumers determines the critical path instructions and Freed in which the number of freed-to-enqueue instructions determines the critical path instructions [3]. In this method, we examine the oldest instructions in issue window and mark them as critical if their source operands are not ready. To enhance speed of processors, critical instructions should use fast resources because they limit the execution time. Non-critical path instructions can use slow resources with negligible penalty in time in exchange for power improvement.

We exploit critical path information in two parts of a Superscalar processor: L1 data cache and integer- and floating point- register files.

Our new L1 data cache is structured into super-sets which are a number of cache rows. Each super-set is provided with nominal and reduced supply voltage and is capable of switching between the two voltages through voltage regulators. The nominal voltage preserves performance and the other supply voltage lowers power with negligible penalty in time.

We decide on supply voltage of super-sets based on critical instructions. The super-sets accessed by more critical load/store instructions and their corresponding analog blocks are assigned to use nominal voltage. On the other side, other super-sets and their corresponding analog blocks are assigned to low voltage supply for power reduction. As such, we reduce power of caches without prolonging execution time of critical instructions.

Our new integer- and floating point- register files are also structured into super-sets. Similar to the new cache, the registers that are accessed frequently by critical instructions are assigned to use nominal voltage to preserve performance. On the other side, registers that are rarely accessed by critical instructions use reduced voltage to lower power consumption. We use two analog blocks powered at different voltage levels and a lookup table containing the voltage information of each super-set. When a register is accessed by a processor, the corresponding analog block is enabled to read or write the register.

In this study, we use HSPICE to model and simulate the operations of the cache and register files. The dynamic and static powers in each cycle are measured through HSPICE and then fed into SimpleScalar for detailed architectural simulations.

#### 1.2 Thesis Overview

The rest of the thesis is organized as follows. In chapter 2, we review related work and discuss a number of circuit-, architectural-, and software- level techniques for reducing power of functional blocks, caches, and register files. In chapter 3, we explain Superscalar processor which is the baseline architecture used in this study. In chapter 4, we elaborate circuit level structures for both L1 data caches and register files utilizing dual supply voltages in details. Critical path instructions and the techniques to identify them in a program are explained in this chapter. In chapter 5, we report simulation results for low-power cache and register file. We also discuss the effect of a number of architectural parameters on power and performance. Finally, we conclude the study and propose the future work in chapter 6.

#### Section 2

#### **Literature Review**

(1) A number of prior techniques exploited critical path instructions to reduce power while preserving performance. H. Yang *et al.* studied software pipelined loops, a compile-time instruction scheduling technique to reduce power [5]. The authors claim that in more than 75% of execution cycles, at least one instruction exists which has slack. A slack instruction is an instruction which its execution can be delayed without impacting performance. They used software pipelining to reschedule instructions in loops so that slack instructions are executed by slow and power efficient functional units.

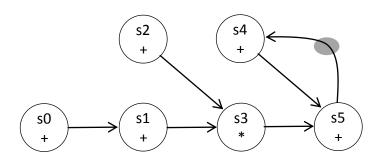

Figure 2-1 shows the data dependence graph of a loop. The nodes of the graph represent functional units in a processor such as adder, multiplier, etc. The edges in the graph represent data flow in the program. For instance, the edge from S2 to S3 shows that S2 produces data that is needed by S3. In this example, a carry-over loop, s5 to s4, is marked by a gray circle and this carry-over loop also is marked in gray cells in Figures 2-2a and 2-2b. We assume that there is no dependency between iterations of the loop. The authors use this example to compare two architectures: Architecture 1 has three fast integer Add units and two fast integer Multiply units (op-code mnemonic: Mult). The latency of Add is one cycle and the latency of Mult is three cycles. Architecture 2 replaces one Add and one Mult in Architecture 1 with slow units. The latency of the slow units is twice the latency of fast units.

In Architecture 1, all resources are fast and Add instruction requires one cycle to execute. Therefore, s2 is issued one cycle ahead of s3. Figure 2-2a shows time steps of this architecture. In Architecture 2 (Figure 2-2b), s2 and s3 are scheduled in the slow Add and Mult units. To reduce impact of slow units on performance, instead of issuing s2 in time step 1, now it is scheduled in time step 0 (2 cycles ahead of s3). Both architectures have the same initiation interval of two, even the s5 to s4 carry-over loop appears later in architecture 2. Initiation interval is the number of clock cycles separating initiation of successive iterations of a loop [23]. That is to say, in both architectures, s0 of consecutive loop iterations are two cycles apart. The overall delay penalty is only two cycles for Architecture 2 regardless the

number of iterations. With more iteration, the power saved by using slow units can overcome the two cycle penalty.

Figure 2-1: Example loop [5].

|           | Time Steps |       |    |       |    |       |    |    |    |    |

|-----------|------------|-------|----|-------|----|-------|----|----|----|----|

| Iteration | 0          | 1     | 2  | 3     | 4  | 5     | 6  | 7  | 8  | 9  |

| 0         | s0         | s1,s2 | s3 |       | s4 | s5    |    |    |    |    |

| 1         |            |       | s0 | s1,s2 | s3 |       | s4 | s5 |    |    |

| 2         |            |       |    |       | s0 | s1,s2 | s3 |    | s4 | s5 |

| (a)       |            |       |    |       |    |       |    |    |    |    |

(a)

|           | Time Steps |    |       |    |       |    |       |    |       |    |    |    |    |

|-----------|------------|----|-------|----|-------|----|-------|----|-------|----|----|----|----|

| Iteration | 0          | 1  | 2     | 3  | 4     | 5  | 6     | 7  | 8     | 9  | 10 | 11 | 12 |

| 0         | s0,s2      | s1 | s3    |    |       |    |       | s4 | s5    |    |    |    |    |

| 1         |            |    | s0,s2 | s1 | s3    |    |       |    |       | s4 | s5 |    |    |

| 2         |            |    |       |    | s0,s2 | s1 | s3    |    |       |    |    | s4 | s5 |

| 3         |            |    |       |    |       |    | s0,s2 | s1 | s3    |    |    |    |    |

| 4         |            |    |       |    |       |    |       |    | s0,s2 | s1 | s3 |    |    |

|           | (b)        |    |       |    |       |    |       |    |       |    |    |    |    |

Figure 2-2: (a) A schedule for architecture a1 (b) A schedule for architecture a2 [5].

- H. Yang *et al.* show that this technique reduces power of functional units up to 31% with a minimal performance impact. However, the shortcoming of software scheduling is that it needs recompilation when the program runs on different machines. On the other side, we focus on hardware solutions which do not require recompilation of programs.

- (2) J. Seng *et al.* used a dynamic critical path predictor to lower the power consumption in functional units and in instruction issue window [6]. This hardware solution allows the

processor to detect phase changes in programs dynamically and is more suitable for a cache design.

They explored various architectural configurations regarding their performance and power improvement. The configurations vary from six fast functional units and zero slow unit to zero fast unit and six slow units. They show that, over 50% of the performance gap between 0-fast/6-slow and 6-fast/0-slow configurations can be filled with only a single fast functional unit. This is due to the fact that the critical path instructions create a chain of dependency one instruction waits for the prior instruction to finish. When the prior instruction is finished, the functional unit is also freed up for the next task. Therefore, with a few fast functional units, it accomplishes most of the work.

One important factor regarding performance and power is the ratio of IPC (instruction per cycle) to power. When power is lowered and/or the performance is improved, IPC to power increases. The authors also explored different number of functional units and various instruction queues regarding both sizes and organizations and benchmarked them with IPC to power ratio. It is found that the advantage of having mostly slow functional units is significant. This confirms the characteristic of a chain of dependency.

One of the shortcomings of their work is that they did not use accurate circuit simulations to extract static and dynamic power of functional units and issue window. On the other side, we model SRAM cells in transistor level and use HSPICE to calculate static and dynamic power and feed them to architectural simulations.

(3) R. Bahar *et al.* exploited the critical path instructions and classified the cache misses into critical and non-critical misses [7]. The non-critical misses are placed in a penalty buffer while critical misses remain in the main cache. The rationale is that the penalty for an  $L_1$  cache miss and retrieval of data from other levels of caches and/or main memory is too costly in terms of time and power. It can be seen in Table 2-1 that L2 cache access in iMac G5 processor takes more than 3 times longer than that of  $L_1$  cache access [28]. If the critical instruction data can be kept longer in the cache against the replacement policy, it improves

both performance and power. They show that this method improves performance of processors by 4% and saves power of  $L_1$  data caches up to 13%. They later on developed a strategy for identifying the latency-tolerant data at runtime and placing them directly into a non-critical buffer, instead of moving cache misses into a penalty buffer as in their prior work [8].

Table 2-1: Memory Hierarchy, iMac G5 [28]

| iMac                    | Reg          | L <sub>1</sub> Inst | L <sub>1</sub> Data | $L_2$         | DRAM         | Disk                       |

|-------------------------|--------------|---------------------|---------------------|---------------|--------------|----------------------------|

| Size                    | 1K           | 64K                 | 32K                 | 512K          | 256M         | 80G                        |

| Latency<br>Cycles, Time | 1,<br>0.6 ns | 3,<br>1.9 ns        | 3,<br>1.9 ns        | 11,<br>6.9 ns | 88,<br>55 ns | 10 <sup>7</sup> ,<br>12 ms |

Their work focuses on both  $L_1$  and  $L_2$  data cache as a whole and reduces power by increasing hit rate of  $L_1$  data cache or by reducing traffic to  $L_2$  cache. The power saved is mainly due to  $L_2$  cache. Our approach is different since we target only  $L_1$  cache by utilizing two different voltage supplies.

(4) R. Balasubramonian *et al.* applied the instruction criticality to L<sub>1</sub> data and instruction caches by partitioning the caches into 2 different banks [9]. The cold banks are slow and low power while the hot banks are fast and power hungry. They steer and place data in the data cache based on the percentage of critical instructions accessing the cache blocks. This instruction and data reorganization however increases the contention and degrades the performance in the conventional caches as it lacks the flexibility of resizing the cache banks to adapt to the variability of programs. For instance, when a section of a running program has more critical load/store instructions, the hot banks may experience frequent data replacement from memory.

Their technique is similar to having two static caches in the system. One is fast and power hungry and the other is slow and power efficient. On the other side, the approach we propose in this work is able to dynamically assign and convert a portion or all of the cache cells into high supply voltage as needed in a running program.

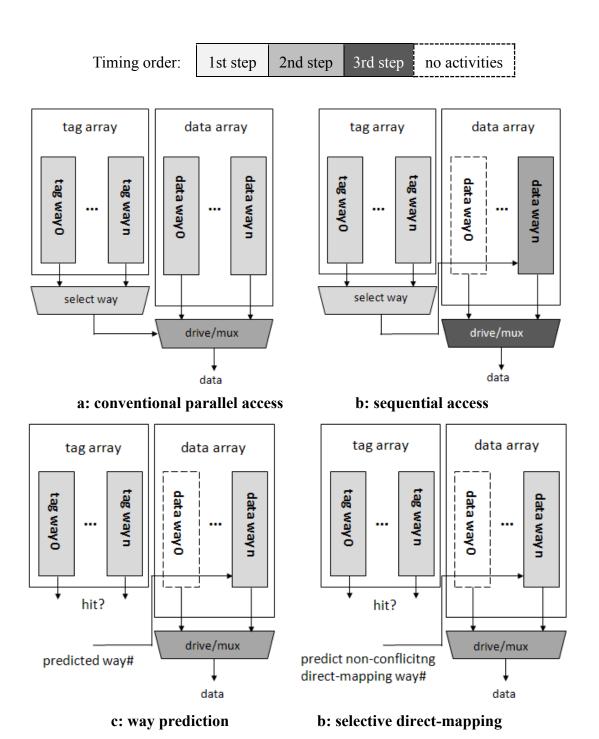

(5) A set-associative cache checks all tags in a set in parallel to accelerate look-up time. However, if there is a hit, only the matching way provides data. As such, the conventional caches waste energy in exchange for lower access time. M. Powell *et al.* exploited way-prediction and selective direct-mapping to access the way that is likely to have the matching tag and to avoid accessing other ways if the prediction is correct [12]. Various set-associative cache access techniques are depicted in Figure 2-3.

Figure 2-3a shows the conventional set-associative cache. All ways are accessed in parallel; however, only the data in the matching way will be multiplexed out to the processor. This wastes (n-1)/n\*100 percent of energy where n is the number of ways. Figure 2-3b shows a sequential technique. In this technique, ways are accessed sequentially. In the first step, way0 is accessed. If a hit happens, data is returned to the processor; otherwise, way1 is accessed. This procedure is repeated for way2 and way3. The main drawback of this method is that it takes longer to retrieve data from cache. In way-prediction (Figure 2-3c), the matching way is predicted based on history of cache accesses. Way-prediction requires searching a history table to determine which way contains the address. The selective direct-mapping cache (Figure 2-3d) has both direct-mapped and set-associative ways. All the cache accesses are categorized as non-conflicting and conflicting. For non-conflicting addresses, we access direct-mapped cache to reduce power. For conflicting addresses, we access set-associative ways to reduce performance degradation.

Way prediction and selective direct-mapping are orthogonal to our work and can be combined with our dual-supply SRAM cells.

Figure 2-3: Access and timing for design options [12].

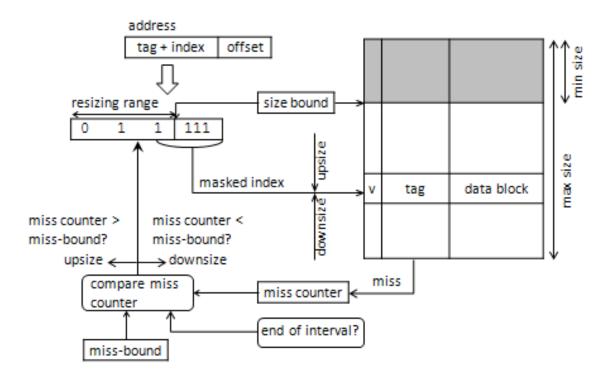

(6) S. Yang *et al.* used an integrated circuit and architectural approach to reduce static leakage current [13]. They proposed to dynamically resize an instruction cache to adapt to application's required size based on the cache miss rate.

Figure 2-4 shows the anatomy of their Dynamically Resizable instruction cache (DRI icache). The miss counter counts the number of cache misses at each instruction cycle. At the end of each interval, depending on whether the miss counter is lower/higher than a threshold, the cache is either upsized or downsized by adjusting the number of masked index bits. The interval may take thousands of instruction cycles.

Figure 2-4: Anatomy of a Dynamically Resizable instruction cache (DRI i-cache) [13].

The unused sections of the cache are virtually turned off to eliminate leakage. By only using a smaller section of a cache and turning off all unused sections, they are able to reduce energy of caches with negligible effect on performance. This method is orthogonal to our optimization technique and can be used in conjunction with our power-aware cache cells to reduce power of caches further.

(7) J. Abella *et al.* proposed two cache architectures using different threshold voltage transistors [29]. One is of nominal threshold voltage (fast transistor) and the other is of high-threshold voltage (slow transistor) to reduce leakage current.

The first architecture is locality-based organization. In this organization,  $L_1$  cache, called Fast Cache, is built using fast transistors.  $L_2$  cache is built using slow transistors; therefore  $L_2$  cache is called Slow Cache. The normal  $L_2$  cache in the system is now called  $L_3$  cache. They assumed the latency of Fast  $L_1$  cache is one while the latency of Slow  $L_2$  cache is two. This architecture factually turns a two level cache system into a three level cache system. Since the penalty of Slow  $L_2$  is less than  $L_3$ , the power can be reduced comparing with the conventional cache organization. However, one can see that when there is an  $L_1$  cache miss, the processor needs to access Slow  $L_2$ . This increases latency of memory hierarchy.

The second architecture is criticality-based organization. In this organization, there are a fast  $L_1$  and a slow  $L_1$  caches. Both of them are always accessed in parallel. If a critical load instruction hits in the slow cache and misses in the fast cache, the data is copied to the fast cache. If a critical load instruction misses in both caches, the data is retrieved from the following level of cache and only is stored in the fast cache. If a non-critical load instruction hits in either caches, data is not copied from one to the other since it is a non-critical load instruction. If a non-critical instruction misses in both caches, the data is then retrieved from the following level of cache and is only stored in the slow cache.

As one can see, comparing with locality-based architecture, total power saving in criticality-based structure is less since it accesses both caches in parallel. In addition, the data copying increases the overhead of this technique. Although criticality-based method may look inferior to the locality-based organization in term of power saving, it still has a significant power improvement comparing with conventional  $L_1$  cache.

Our approach on the other hand, doesn't require complicated data copying or parallel cache look-up. Our cache can be accessed normally while capable of reducing power by converting sections of the cache to low-power cells.

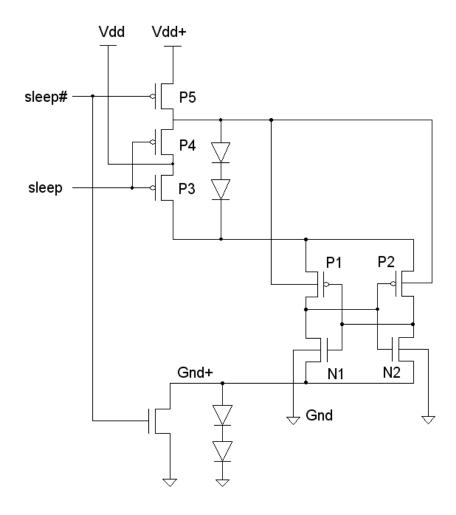

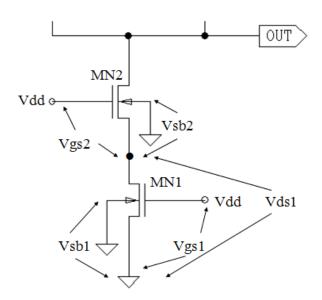

(8) H. Hanson *et al.* utilized Multi-Threshold CMOS to reduce static energy in caches [17]. The sub-threshold leakage current depends on both temperatures (T) and transistor's threshold voltage (Vt) as indicated in the following equation.

$$I_{leak} \propto e^{\left(\frac{-Vt}{T}\right)} \tag{2-1}$$

Therefore, the higher the threshold voltage is, the lower the leakage current. The Threshold voltage can be expressed as a function of  $V_{SB}$ ; the voltage difference at a transistor's source and bulk/substrate which is indicated in the following equation:

$$Vt = Vt0 + \gamma \left( \sqrt{|2\Phi_{E}| + V_{SB}} - \sqrt{|2\Phi_{E}|} \right)$$

(2-2)

where Vt0 is the threshold for zero substrate bias (V<sub>SB</sub>=0),  $\gamma$  denotes the body effect coefficient and  $2\Phi_F$  is the surface potential [18].

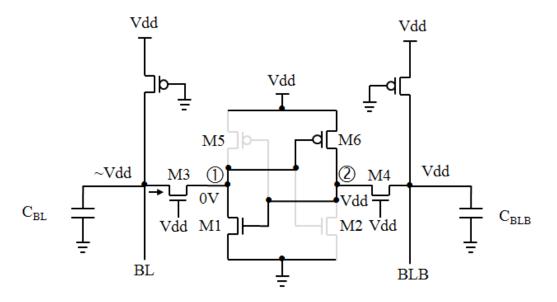

Figure 2-5 is the schematic of their circuit to increase threshold voltage. When in sleep mode, the sleep signal is high, P3 and P4 are turned off, and P5 is turned on. This makes the body/bulk of P1 and P2 tied to Vdd+ while their source nodes are tied to two diodes. This boosts up PMOS's  $|V_{SB}|$  and therefore, its threshold voltage increases. When it is not in the sleep mode, P3 and P4 are turned. Therefore, it connects the source nodes and the body/bulk of P1 and P2 to Vdd. In this mode,  $|V_{SB}| = 0$ ; therefore Vt = Vt0.

The same analysis can be easily followed for N1 and N2. This circuit which consumes a small portion of a cache's total power reduces static power. On the other side, our approach mainly focuses on the dynamic power.

Figure 2-5: MTCMOS SRAM cell schematics [17]

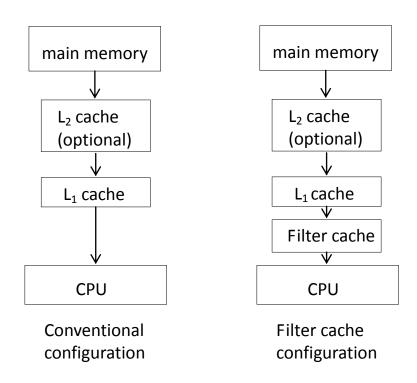

(9) J. Kin *et al.* proposed a filter cache structure [19] to reduce power consumption in caches. Their filter cache is another cache which is significantly smaller than traditional  $L_1$  cache. Due to its smaller size, the capacitive load on bit line and bit line bar of the SRAMs is much smaller and therefore provides shorter access time. Also, due to less capacitive load on bit line and bit line bar, it consumes less power than the traditional  $L_1$  cache. Figure 2-6 shows the filter cache.

The down side for this structure is that the filter cache has higher miss rate than  $L_1$  cache. When a miss happens, the processor needs to sequentially access  $L_1$  cache which elongates the data hit time. The author's hypothesis is that the reduction in power consumption will

compensate the performance loss and results in a lower energy×delay product. Due to the possible high miss rate, the authors also suggest that this filter cache can be turned off or bypassed when higher performance is needed.

This filter cache design may look similar to the locality-based cache organization proposed by J. Abella *et al.* [29] which was discussed earlier in this section. However, in locality-based cache organization, the second level of  $L_1$  cache is a slow cache. By utilizing critical path prediction, the instructions are placed in either fast  $L_1$  or slow  $L_1$  to achieve power reduction with minimum performance loss. Here, J. Kin *et al.*'s structure utilizes the smaller capacitive load on bit line and bit line bar to achieve the same goal. Filter cache is orthogonal to our optimization techniques and can be used in conjunction with our SRAM cells to reduce power of caches further.

Figure 2-6: Traditional cache vs filter cache [19]

(10) C. Su *et al.* proposed block buffering to reduce power consumption in caches [20]. This technique is similar to the filter cache proposed by J. Kin *et al.* [19]. It saves power by using a buffering cache which is faster and more power efficient than  $L_1$  cache. In C. Su *et al.*'s analysis, this structure is beneficial to the applications with high spatial locality patterns. Spatial locality is also called locality in space. It means that if an addressed in cache is referenced, the nearby addresses will be referenced soon.

They also proposed a cache sub-banking structure. Conventionally, when a cache is accessed, the entire cache line/row is accessed. For instance, for a 64kB cache with 64 Byte cache line, the whole 64-byte is read or written at the same time. If the location of the requested data in the 64-byte cache line is known, then there is no need to access unrequested data in the same cache line. Figure 2-7 depicts the sub-banking cache structure.

Figure 2-7: Structure of a sub-banking cache [20]

Their approach is orthogonal to our optimization technique and can be used in conjunction with our cache cells to reduce power of caches further.

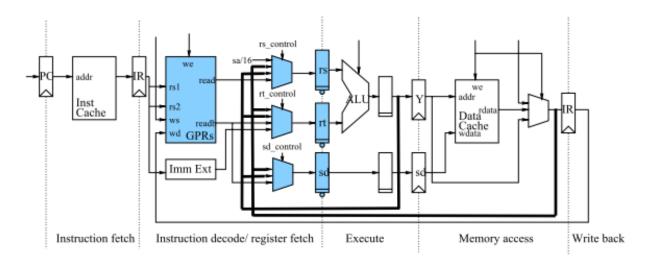

(11) S. Park *et al.* reported that register files are hot spot units and may consume up to 25% of total processor power when running embedded programs [21]. J. Tseng *et al.* found that on average, 36% of instructions get their source operand values from forwarding bus [22]. This implies that 36% of register file power is wasted. Figure 2-8 shows architecture of a MIPS (Microprocessor without Interlocked Pipeline Stages) processor. The data bypassing/forwarding paths are drawn in bold lines. It clearly points out that the register file is accessed at early instruction decode stage. At the late instruction decode stage, the multiplexers determine whether the source operand values should come from forwarding bus. If data comes from forwarding bus, then the data read from register file are discarded. If this type of unnecessary reads can be avoided (bypass-skip) or the register file is only accessed when there is no data bypassing path (on-demand reads), the power is reduced. J. Tseng *et al.* reported that the bypassing-skip technique leads to an average of 16% of power saving.

Figure 2-8: MIPS pipeline processor [21]

Traditionally, processors try to separate data dependent instructions as much as possible through inserting non-dependent instructions between them. This is necessary to avoid read-after-write hazards. S. Park *et al.* utilized the bypass-skip technique proposed by S. Tseng *et al.* along with a bypass sensitive algorithm to reduce the number of register file accesses. In their bypass sensitive algorithm, instead of separating data dependent instructions, they try to

schedule them as close as possible, so that most of the operand values are bypassed from other stages instead of coming from register files. Their heuristics shows 12% reduction in register file reads.

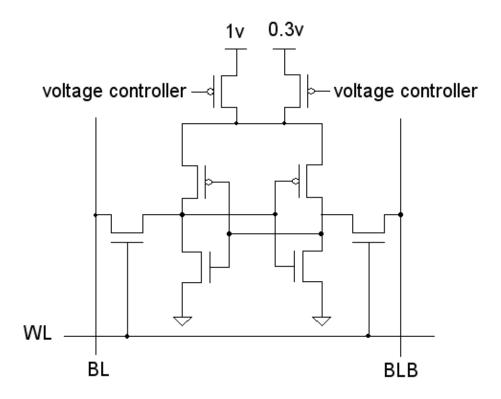

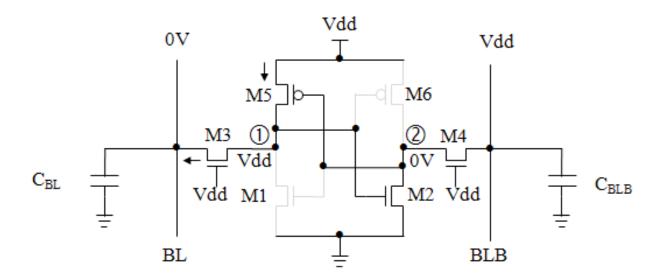

(12) J. Ayala *et al.* [31] proposed a technique which reduces the power consumption in register files by putting unused registers to a drowsy state with the support of compiler [32]. X. Guan *et al.* also proposed a similar technique [33]. Figure 2-9 shows their modified drowsy register file cell. This cell can be supplied by either 1v or 0.3v through selecting one of the two PMOS transistors on top of the Figure. When 0.3v is selected, the voltage is too low for the cell to operate (write or read) but is high enough to retain the cell's data. Once the cell is woken up by setting the 1v supply voltage, it can operate normally.

To support this design, they extend ISA with two additional instructions; one turns a set of registers to the drowsy state and another wakes up registers to normal mode. The compiler is responsible to use these instructions to manage register file reconfigurations. In the code generation phase, the compiler needs to detect hot spot regions such as loops and repeated functions and mark the beginning and the end of such regions. For these regions, the register file cells are set to use 1v supply voltage. For other regions, the register file cells are set to use 0.3v supply voltage. As such, power consumption of register file is reduced.

The authors also point out that turning the individual register on and off results in significant timing overhead and degrades performance. They propose turning a group of registers on and off to reduce overhead of this technique. They reported 40% reduction in power of register file with groups of 16 registers.

One of the drawbacks of this method is that it requires recompilation when the code is run on a different machine. Our approach, however, exploits the critical path information which doesn't need the compiler. Another difference is that their drowsy state only retains data while in our approach, the register cells function normally (write and read) at the low supply voltage with only one cycle penalty in time.

Figure 2-9: A drowsy register file cell [31]

(13) N. Gong *et al.* [35] pointed out that status of a register changes over time: empty, idle, ready and free. For example, when an instruction is renamed, its architectural register is mapped to a physical register, say R1 is mapped to P1. P1 then changes from a free state to an empty state due to this mapping. As the instruction executes, the status of P1 changes from empty state to ready state which allows write and read operations. When the last consumer instruction reads from P1 and before P1 is reclaimed back to the free list, P1 turns into an idle state. When the architectural register R1 is remapped, P1 is released and is retuned to the free list.

When the physical register is in ready state, the register must function normally. However, in empty state or idle state, the register can be put into a drowsy state to retain data and to reduce the leakage current. While the register is in free state, the register can be shut off to minimize the leakage current.

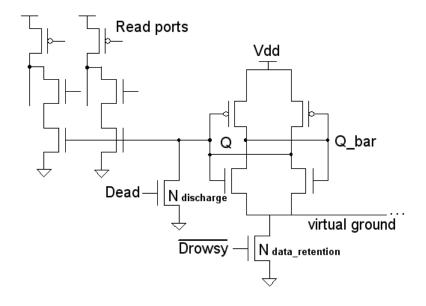

Motivated by different states of a register, they utilize gated-ground technique proposed in [36] to reduce static power in register file [35]. In their work, there are 3 states similar to [34]: work, drowsy, and dead state. Figure 2-10 shows the circuit of a low power cell.

When the cell is in work state (dead=0, drowsy=0), N<sub>discharge</sub> is cutoff and N<sub>data\_retention</sub> is on. So, the cell works normally. In the drowsy state (dead=0, drowsy=1), N<sub>data\_retention</sub> is cut off and the voltage at the node (either Q or Q\_bar) reaches a saturated voltage when it stores "0". Through proper transistor sizing, this saturated voltage will not be high enough to disturb the node when it stores "1" (turning on the NMOS in the branch which stores "1"). Therefore, the data is retained successfully. However, due to the stacking effect [37], the leakage current is reduced substantially. According to stacking effect, the leakage current through a 2-transistor stack is roughly an order of magnitude higher than that of a single transistor. The dead state (dead=1, drowsy=0) provides minimum leakage current by discharging the cell to "0". This is due to the fact that the leakage current of a cell storing "0" is smaller than the leakage current of a cell storing "1".

Their experiments show 12.7-14.1% power reduction in ROB-based (Re-Order Buffer based) microprocessors and 12.4-17.9% power reduction in checkpoint-based microprocessors. Our approach is different since we mostly focus on dynamic power of register file.

Figure 2-10: A gated ground register file cell [35].

#### **Section 3**

## **Super-scalar Processor Architecture**

In this chapter, we discuss architecture of a superscalar processor briefly as it is the target architecture of this study. Section 3.1 explains how modern processors exploit instruction level parallelism. Sections 3.2 to 3.5 discuss the main stages of a superscalar processor: fetch, dispatch, issue, write-back and commit.

#### 3.1 Introduction

Over the past several decades, computer technology has improved rapidly. This rapid improvement is the result of advances in semiconductor technology and innovative architectural techniques. Transistor shrinking has made it possible to build processors with multi-GHz clock frequency. The feature size of transistors reduced from 10um in 1970 to 28nm in 2011 [43], increasing clock frequency from a few Mhz to over 3 Ghz [44, 45].

One way to boost performance of processor is exploiting instruction level parallelism (ILP). Pipelining was one of the first architectural techniques which used parallelism in hardware. A pipeline processor is composed of several stages and these stages process instructions concurrently. This technique was initially developed in the late 1950's and became popular in large scale computers during the 1960's [24].

Figure 3-1a shows execution of a program in a processor that does not exploit ILP. Figure 3-1b shows the same program in a pipelined processor. We assume that each instruction goes through three stages: Instruction-Fetch (IF), Execute (EX), Write-Back (WB). In Figure 3-1a, instructions execute sequentially. This would take a total of 9 cycles to execute all three instructions. However, in Figure 3-1b, instructions execute in parallel. As soon as one instruction finishes up a stage, immediately the next instruction starts. By overlapping execution of instructions, the same instructions execute in five cycles.

```

C1 C2 C3 C4 C5 C6 C7 C8 C9

LD

R1, 0(R2)

IF EX WB

DSUB R4, R1, R5

IF EX WB

AND

R6, R1, R7

IF EX WB

(a)

C1 C2 C3 C4 C5 C6 C7 C8 C9

LD

R1, 0(R2)

IF EX WB

DSUB R4, R1, R5

IF EX WB

R6, R1, R7

IF EX WB

AND

(b)

```

Figure 3-1: (a) An example of sequential execution. (b) An example of pipelined execution.

It's worthy to note that, in the pipelined example, the latency of an instruction is not shortened or improved. However, the throughput is significantly improved. This enhances the performance of processors as it takes less time to execute programs.

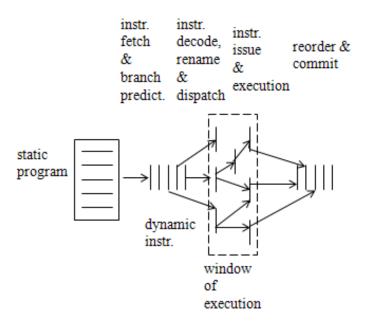

One of the limitations of a pipeline processor is that it fetches and executes at most one instruction per cycle. Therefore, the maximum performance of a pipelined processor is one instruction per cycle (IPC=1). A superscalar architecture improves performance of a pipelined processor by issuing multiple instructions per clock cycle. Likewise, a superscalar processor separates an instruction's lifetime into different phases. However, in contrast to the pipelined processor, each phase may have multiple instructions per cycle. Figure 3-2 summarizes execution flow in a superscalar processor. Instructions are fetched from a static program. The fetch stage uses a branch predictor to speculate the outcome of branch instructions. This stage generates a stream of dynamic instructions which is fed to the rest of processor. These dynamic instructions are inspected for any data dependences which may cause a processor to stall. The false data dependences (output and anti-dependences) are removed by register renaming to leave only the true data dependences. In the next step, the

stream of instructions is dispatched into issue window. In the issue window, instructions wait until their source operands become ready. Once source operands are ready, instructions are sent to free functional units for execution. From this stage, independent instructions may execute out of order. Instructions with true data dependences need to execute in order to guarantee correct outcome of programs. At the end, all the instructions are re-ordered and commit. In this last stage, if a branch misprediction is detected, all speculative instructions are squashed and instruction from the correct path are fetched and executed.

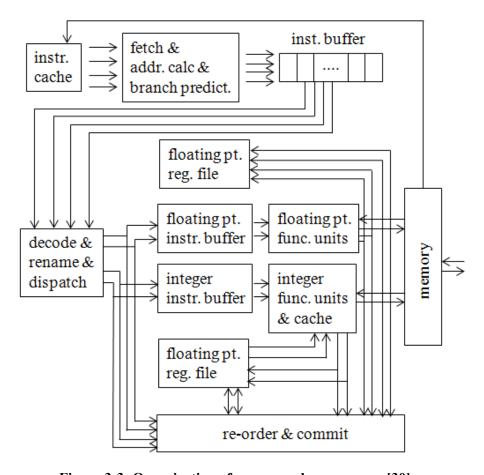

Figure 3-3 shows details of a superscalar processor. The main stages of the processor are: fetch, dispatch, issue, execution and commit. In the following sections, we will discuss each stage in details.

Figure 3-2: A conceptual execution flow of a superscalar processor [26]

Figure 3-3: Organization of a superscalar processor [30]

#### 3.2 Instruction fetch

The fetch unit reads instructions from memory and sends them to the rest of superscalar processor. Since main memory is slow, processors use cache, which is a small and fast memory unit, to reduce latency of memory. The address of instructions comes from Program Counter (PC). Instruction cache is searched with PC and if an instruction pointed to by PC is not found in the cache, then a cache miss occurs and memory should provide the instruction.

In fetch stage, PC is incremented to point to the next instruction. However, if a branch instruction exists in the program, then PC should be loaded with target address. If the processor stalls until the outcome of the branch is known, then it may take several cycles. Hence, modern processors incorporate branch predictors to overcome the delay of branch

instructions. If the branch is predicted correctly, then the processor continues executing instructions without interruption. If the prediction is wrong, then all instructions that have been executed speculatively should be squashed and the program will restart from the correct branch target. The simplest policy for branch prediction is Taken policy. Taken policy works very well for structures such as loops in programs. In a loop, the program jumps to the start of the loop several times before it exits the loop. Therefore, a Taken policy may be sufficient for loops in programs. However, for other control structures such as if-then-else statement, Taken policy may result in too many mispredictions. There are many other branch predictors [46, 47] which improve accuracy of Taken policy, but this is not the scope of this study.

Instructions fetched from memory are stored in an instruction buffer. The number of instructions fetched per cycle is usually higher than the instruction execution rate to ensure an uninterrupted flow of instructions. When instruction cache miss occurs the fetch unit may stall for a few cycles. Hence, to sustain continuous flow of instructions to the rest of processor, the fetch unit should fetch multiple instructions per cycle.

# 3.3 Instruction decode, rename and dispatch

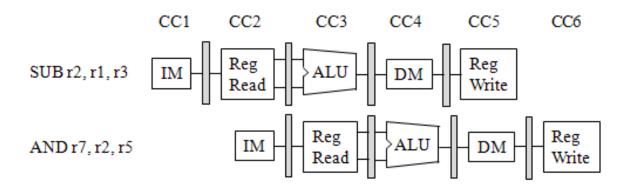

In a single-cycle processor, an instruction reads its source operands from a register file, executes, and then writes the result back to the register before the next instruction is fetched. The data dependence does not create hazard in such a machine. However, in a pipelined processor, this is not true. Before an instruction writes the result to the register file, the next instruction may already be in execution stage with a wrong source operand. Figure 3-4 depicts an example of data hazard. The first instruction, SUB, writes r1-r3 to r2 at clock cycle 5 (CC5 in the figure). However, at clock cycle 5 the second instruction, AND, has already passed register read stage. Therefore, AND instruction gets the old data which is incorrect. One way to overcome data hazard is forwarding. As soon as SUB is executed, the result is forwarded to the AND [48].

Figure 3-4: An example of data hazard [48].

In an out-of-order execution processor such as a Superscalar processor, the order of instructions may change in run-time and this may create new types of hazards. Figure 3-5a. shows a program with five instructions. MULD and ADDD write to the same register: F6. This is called output dependence. An out-of-order execution processor should not change the order of instruction with output dependence; otherwise, write after write (WAW) hazard is created. The other type of dependence is anti-dependence and it happens when an instruction reads from a register and later on, the same register is written by another instruction. For example, in Figure 3-5a, there is anti-dependence between SUBD and MULD because of F8. An out-of-order executing processor should not change the order of these two instructions; otherwise, write after read (WAR) hazard is created.

One way to eliminate output and anti-dependences (also called false dependences) is register renaming. Through register renaming, it is guaranteed that WAW and WAR hazards never happen. As such, a superscalar processor is able to change the order of instructions and reduce execution time. We elaborate register renaming through an example.

To eliminate output-dependence between MULD and ADDD, in Figure 3-5b, register F6 in MULD is renamed to P1. Any other instruction that depends on MULD, i.e. ADDD, uses P1 instead of F6. Now, ADDD does not need to wait until MULDD finishes. Since the output-dependence is removed, a processor is free to execute ADDD sooner than MULDD. This may reduce execution time of the program. Similarly, we can use register renaming to

eliminate anti-dependence. In Figure 3-5b, register F8 in SUBD is renamed to P2. Hence, SUBDD does not wait until MULD reads its source operands. It can start and even finish before MULD reads its source operands.

Figure 3-5: Register renaming

There are two register renaming techniques commonly implemented in microprocessors. The first uses a physical register file larger than the logical register file. The logical registers, also called architectural registers, are those registers used in a static program while the physical registers are those in the microprocessor. To track the mapping of logical registers to the physical registers, the processor uses a register renaming table. This table is indexed by logical registers and each entry of this table shows the physical register corresponding to a logical register.

When an instruction is decoded, the processor takes a physical register from the list of free physical registers and assigns it to the destination field of the instruction. Also, the register renaming table is updated. As part of renaming process, the physical register is then removed from the free list. The physical register is only reclaimed and placed back into the free list when the assigned physical register has been read and its corresponding logical register has been renamed to another physical register.

Figure 3-6 is an example of the physical register reclamation. The logic register F6 in MULD instruction in Figure 3-6a is renamed and mapped to physical register P1. F6 in ADDD instruction is renamed and mapped to P6. SD uses P1 as its source operand. Therefore, P1 can be reclaimed and placed back into free list only when ADDD instruction commits. Only at that time, we are sure that P1 is not needed by any other instruction.

Figure 3-6: Physical register reclamation

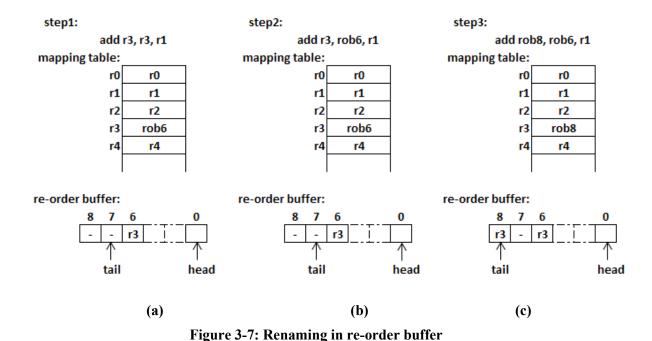

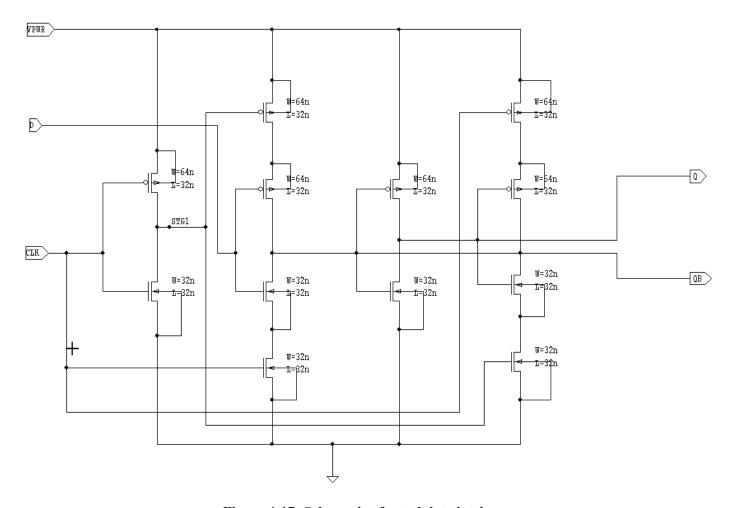

The second method of register renaming is to use a re-order buffer. Re-order buffer is implemented in a processor as a circular buffer with head and tail pointers. When an instruction is dispatched, it is inserted to the tail entry of the re-order buffer. The result (value of destination operand) of the instruction is written into the assigned entry in the re-order buffer. In the renaming process, the logical source operands are used to access a mapping table to locate the source operands. We use the example in Figure 3-7 to illustrate this.

Before the instruction add r3,r3,r1 is dispatched, r0~r2 and r4 reside in register files and r3 resides in re-order buffer #6 (rob6) as depicted in Figure 3-7a. At this point, the head of re-order buffer points to entry #0 in the re-order buffer and the tail points to #7. When the instruction add is dispatched, the processor uses its source operands to access the mapping table and locate the locations of their values as this value can be either in register file or in another entry of the re-order buffer. In this case, the value of r1 resides in register file (r1) and the value of r3 resides in re-order buffer #6 (Figure 3-7b). The add instruction is then placed in re-order buffer #8 by the processor and the tail pointer is moved to point to entry #8 (Figure 3-7c). Since its result will be inserted into re-order buffer #8, the instruction is renamed to "add rob8, rob6, r1" and the mapping table is updated accordingly as in Figure 3-7c.

# 3.4 Instruction issue and parallel execution

After register renaming, instructions are issued to functional units. At this stage, the processor checks for availability of data and resources. Ideally, when the input operands are ready, the instruction can be issued. However, in reality with limited hardware resources, some of the instructions may be stalled until resources are freed up.

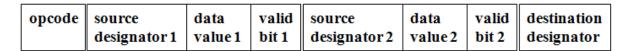

There are a number of ways of organizing instruction issuing buffers. The most common one in superscalar processor is to use reservation station (RS). Reservation station is a set of buffers and each buffer holds an instruction. Figure 3-8 shows fields of an RS buffer. When an instruction is dispatched to an RS buffer, source operands are read from register file if they are ready (e.g. r1 in Figure 3-7b). If the source operands are not ready, then the instruction is written into RS and constantly monitors completing instructions. If designator of a completing instruction matches designator of a source operand, then the value on the bus is copied into source operand's data value (Figure 3-8) and the valid bit of the source operand is set to indicate the readiness of the operand. When all the source operands are ready (valid bits are set), the instruction is ready to issue.

Notice that to increase Instruction Level Parallelism (ILP), multiple instructions can be issued at the same time in a superscalar processor, provided that there are enough hardware resources.

Figure 3-8: A typical reservation station

Figure 3-9: A multiple reservation station queue

# 3.5 Memory and cache

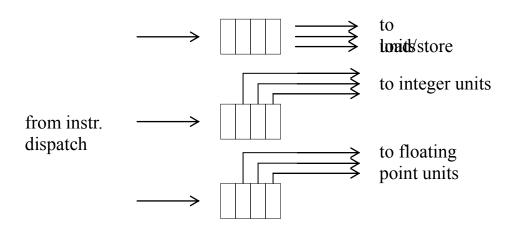

#### 3.5.1 Memory gap

Over the past decades, the performance of processor and memory increased rapidly. However, the performance of processor increases much faster than memory. This resulted in increasing gap between processor and memory (Figure 3-10). One way to reduce this gap is to put a small and fast memory unit, which is called cache, between processor and main memory.

Caches are able to exploit principle of locality and hide latency of memory. According to locality, programs tend to use instructions and data that they have used recently. An

implication of locality is that we can predict which instructions or data will be used in near future based on recent instructions or data.

There are two types of localities: time and space. Locality in time means that if an address (address of instruction or data) is referenced now, it is likely to be referenced again shortly. Therefore, if we write recently accessed addresses in cache, the performance is greatly improved. In a computer program, one example of locality in time is loop. When a processor executes a loop, it generates the same instruction addresses over different iterations of the loop. Locality in space means that once an address is referenced, its adjacent addresses are likely to be referenced in the near future. To exploit locality in space, when a cache miss occurs, a chunk of consecutive addresses are transferred from main memory to the cache. An example of locality in space is an array. When a program processes an array, it usually accesses elements of the array sequentially. As such, when a cache miss occurs, in addition to the missed address, we read nearby addresses from memory and transfer them to the cache.

Figure 3-10: Memory gap [49]

In the following two subsections, we present two types of caches: direct-mapped cache and set-associative cache.

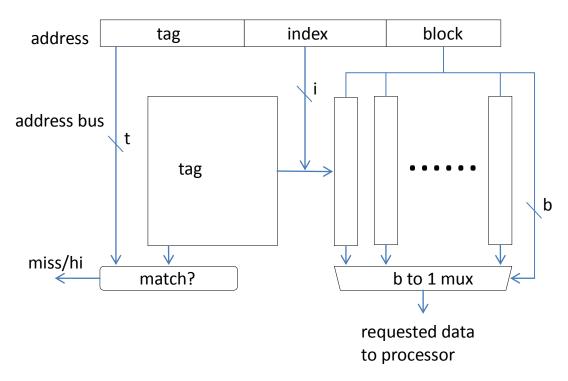

#### 3.5.2 Direct-mapped cache

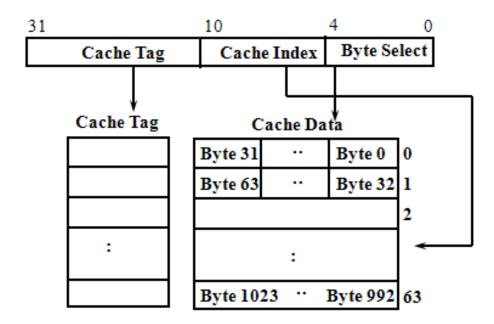

In direct mapped cache, each memory address is mapped to exactly one location in the cache. The address is divided into three fields: cache tag, cache index and byte select. The cache tag is used to determine if there is a cache hit or miss. The cache index is used to determine which cache row possibly contains the address. The byte select is used to select the byte within the cache block. To illustrate this, Figure 3-11 depicts a 2K-byte cache with 32-byte cache blocks.

Since cache block is 32-byte, byte select field requires 5-bit. For a total size of 2K byte direct-mapped cache with 32-byte cache block, there are a total of 64 rows (2048/32 =64). Therefore, the cache index field contains 6-bit. The rest of the address bits form the cache tag.

Figure 3-11: A 2k byte, 32 bit address, direct-mapped cache

Since cache is smaller than main memory, multiple addresses are mapped to the same cache row. We can determine which memory address is mapped to a cache block by comparing cache tag with tag field of memory address. For example, for the 2K-byte cache in Figure 3-11, address 6306 (14b'11 000101 00010) maps to byte number 2 (5b'00010, the

5 lowest bits in address) in row number 5 (6'b000101, the next 6 lowest bits in address). Address 4258 (14b'10 000101 00010) also maps to the same location in cache. However, the tag fields in the two addresses are different.

Notice that to exploit locality in space, the cache writes and reads the whole cache block/row at once.

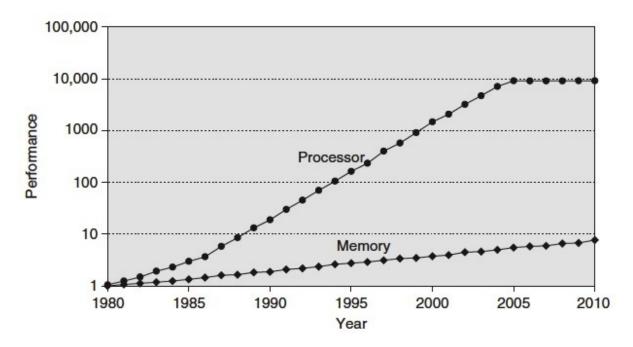

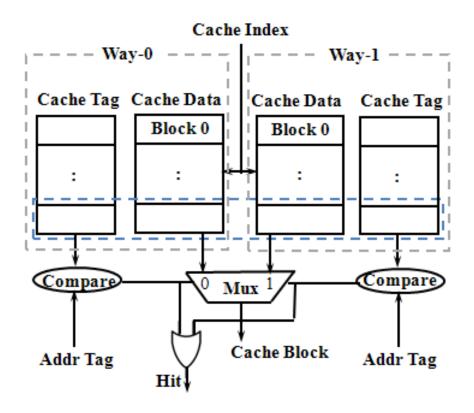

#### 3.5.3 Set-associative cache

One of the limitations of direct-mapped cache is conflict misses. Since each memory address is mapped to exactly one location in cache, the probability of aliasing is high. One way to reduce aliasing in direct-mapped cache is using multiple "ways" in the same cache row. This is the organization of a set-associative cache. In other words, a set-associative cache can be treated as multiple direct-mapped caches running in parallel. Figure 3-12 exemplifies the structure of a 2-way set-associative cache.

In Figure 3-12, way-0 and way-1 have the structure of a direct-mapped cache. During cache look-up, all the ways that cache index points to are accessed in parallel. The cache tags from all ways are compared with tag field of memory address in parallel. If one of the ways has a tag match, it is a cache hit and the corresponding data is passed through a multiplexor to the processor; otherwise, it is a miss. This structure greatly improves the cache hit rate relative to a direct-mapped cache since in the set-associative cache, there are multiple "ways" for an address, instead of just one.

The down side for a set-associative cache is power consumption. For cache look-up, "all" the ways are accessed in parallel. However, only the way that has the matching address provides data. Other ways end up wasting energy.

In the event of cache miss, the cache controller should decide which cache block should be replaced. There are several policies for replacement. The commonly used one is Least Recently Used (LRU) policy. In this policy, the least recently used way will be replaced with new address.

Set-associative cache is the target organization in this study.

Figure 3-12: A 2-way set-associative cache

# 3.6 Commit

The final stage of a superscalar processor is commit. In this stage, all instructions are processed in order to implement the appearance of a sequential model. Also in this stage, a processor can determine whether a branch instruction is mispredicted. If misprediction has occurred, then speculative instructions should be removed from processor and instructions from the correct path should be fetched and executed. To commit an instruction, its result is written back to the register file or to the main memory and its entry is removed from the reorder buffer.

# **Section 4**

# Low Power Cache, Low Power Register File, and Critical Path Instructions

In this chapter, we cover the details of low power cache and register file. In section 4.1, we discuss basics of an SRAM cell, its operation and structure of a cache in circuit level. In section 4.2, we present the structure of the low power cache proposed in this study. In section 4.3, we explain the architecture of the low power register file. In section 4.4, we discuss critical path instructions.

## 4.1 SRAM basics

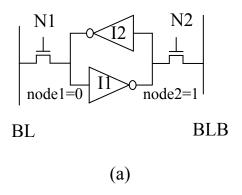

#### 4.1.1 Standard 6T SRAM cells

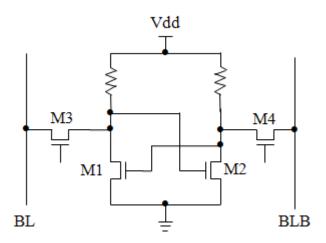

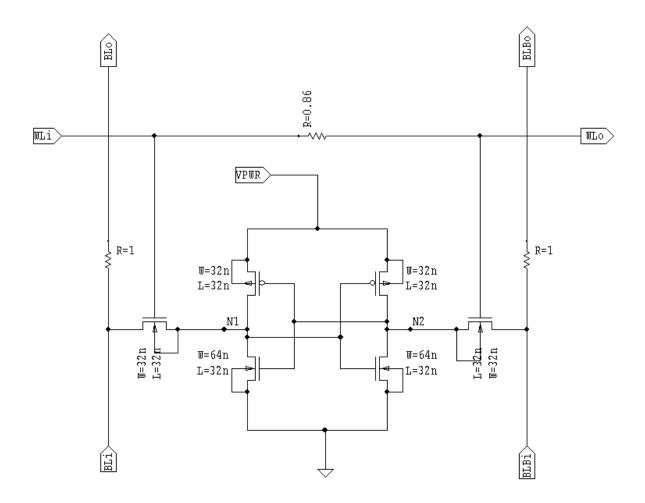

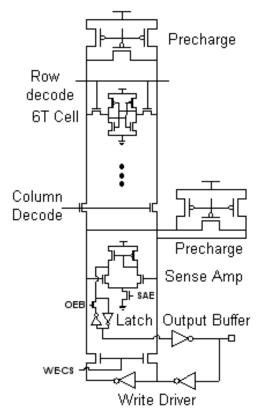

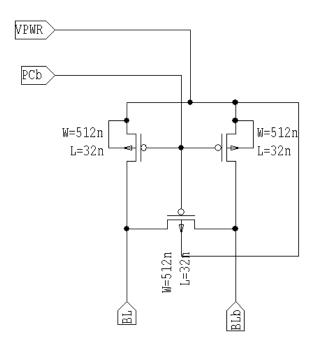

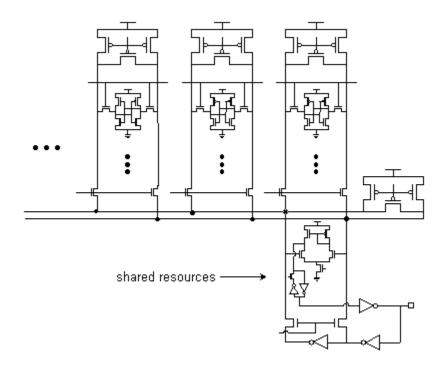

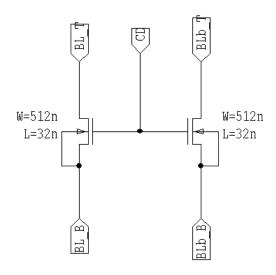

Figure 4-1a depicts the core of a 6T (6 Transistor) SRAM cell. The cell is composed of two inverters connected head to tail. The two inverters form a positive feedback loop to latch data. If node 1 stores "0", then the output of I1 is "1". Input "1" of I2 re-enforced "0" in node1. To read from the SRAM cell, there are 2 NMOS pass transistors on each side. When these two transistors are turned on, node 1 and node 2 can be written or read through BL and BLB, respectively. Figure 4-1b is the 6T SRAM cell in transistor level.

Figure 4-1: An SRAM cell

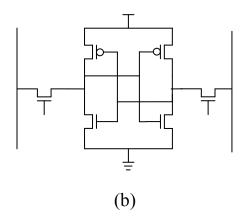

# 4.1.2 4T2R topology SRAM cells

There is another type of SRAM cell: 4T2R. In this topology, the two top PMOS transistors are replaced by two resistors as depicted in Figure 4-2.

Figure 4-2: A 4T2R SRAM cell.