## **Optimum Switch Sizing for Class DE Amplifier**

by Thinh Ngo

A Thesis

Presented to Lakehead University in Partial Fulfillment of the Requirement for the Degree of Master of Science

in

Electrical and Computer Engineering

Thunder Bay, Ontario, Canada

November 9, 2018

## Abstract

Recently, integrated class DE amplifiers without matching networks have been proposed as a compact solution to drive a multi-element piezoelectric ultrasound transducer array for highintensity focused ultrasound (HIFU) therapy. These transducers produce acoustic energy that translates into heat for tissue ablation. In order to steer the focal zone, each element in the transducer array is driven at a different phase. Hence, there's a need for the power amplifier with a digital control unit in this application.

Since each element in the transducer array has a different electrical characteristic and they have to be driven at the same frequency, it is a challenge to drive all transducers in the array at their optimum conditions. This work introduces strategies to determine efficient driving parameters for an entire transducer array. In addition. a method to improve the power efficiency of the class DE amplifier by choosing the optimum size for switching MOSFETs is also proposed. During the operation of a class DE amplifier, losses are caused by the ON resistance and the drivers of the MOSFET gate capacitances. These parameters are directly dependent on the size of the switching MOSFETs. A wider MOSFET will have a higher gate capacitance, but lower ON resistance. With the correct sizing, these losses can be greatly reduced to improve power efficiency and prevent excessive heating. The challenge with this method is the wide selection of transducers with varying impedance. As the load impedance changes, the MOSFET size also needs to be changed to maintain the maximum power efficiency. Also, the proposed design must deliver at least 1 W output power to the transducer in order to produce enough acoustic pressure. This output requirement will limit the available technology that can be used to design the amplifier. In addition, this work also proposes a new driving circuit that consumes less power to operate, and also allows a full 0-360 degree phase shift.

The design is simulated with Spectre simulator using 0.35  $\mu m$  50V CMOS process data available from Austria Micro Systems. The proposed design can deliver 1422mW of average power to 6-elements transducer array, and achieve up to 91% power efficiency.

## Acknowledgments

I would like to thank you Lakehead University and CMC Microsystems for supporting this work. This thesis would not possibly be made without the guidance from my supervisor, Dr. Christoffersne, and my co-supervisor, Dr. Zhou. I also would like to thank my family, especially my mom for supporting me during my hard time to complete this thesis.

Thinh P. Ngo

tngo@lakeheadu.ca

# Contents

| Li       | List of Figures v     |                                              |          |  |  |  |

|----------|-----------------------|----------------------------------------------|----------|--|--|--|

| Li       | List of Tables ix     |                                              |          |  |  |  |

| Li       | st of                 | Symbols                                      | xi       |  |  |  |

| Li       | st of                 | Abbreviations                                | xi       |  |  |  |

| 1        | $\operatorname{Intr}$ | oduction                                     | <b>2</b> |  |  |  |

|          | 1.1                   | Motivations and Objectives                   | 2        |  |  |  |

|          | 1.2                   | Thesis Overview                              | 3        |  |  |  |

|          | 1.3                   | Contribution                                 | 3        |  |  |  |

| <b>2</b> | Bac                   | ground Information and Literature Review     | 4        |  |  |  |

|          | 2.1                   | Introduction                                 | 4        |  |  |  |

|          | 2.2                   | Transducer Characteristic                    | 5        |  |  |  |

|          | 2.3                   | Previous Work on RF Amplifiers               | 7        |  |  |  |

|          |                       | 2.3.1 Class A, B and AB amplifiers           | 7        |  |  |  |

|          |                       | 2.3.2 Class D amplifier                      | 9        |  |  |  |

|          |                       | 2.3.3 Class E Amplifier                      | 14       |  |  |  |

|          |                       | 2.3.4 Class DE amplifier                     | 17       |  |  |  |

|          |                       | 2.3.5 Summary                                | 21       |  |  |  |

| 3        | Stra                  | tegies to Drive Ultrasound Transducer Arrays | 23       |  |  |  |

|          | 3.1                   | Introduction                                 | 23       |  |  |  |

|   | 3.2         | Amplifier Analysis                                                                                           | 23               |

|---|-------------|--------------------------------------------------------------------------------------------------------------|------------------|

|   | 3.3         | Method I - Driving Parameters for Efficiency                                                                 | 28               |

|   |             | 3.3.1 Introduction $\ldots$ | 28               |

|   |             | 3.3.2 Transducer Characterization                                                                            | 29               |

|   |             | 3.3.3 Determination of Driving Parameters                                                                    | 29               |

|   |             | 3.3.4 Simulation and Experimental Results                                                                    | 31               |

|   | 3.4         | Method II - Driving Parameters for Equal Power                                                               | 36               |

|   |             | 3.4.1 Introduction                                                                                           | 36               |

|   |             | 3.4.2 Transducer Characterization                                                                            | 37               |

|   |             | 3.4.3 Determination of Driving Parameters                                                                    | 39               |

|   |             | 3.4.4 Simulations and Experimental Results                                                                   | 40               |

|   | 3.5         | Discussion                                                                                                   | 43               |

| 4 | Dma         | an agad Drivan Dagima                                                                                        | 17               |

| 4 | <b>4</b> .1 | I and B                                                                                                      | <b>±</b> 7<br>47 |

|   | 4.1<br>4.2  |                                                                                                              | 48               |

|   | 4.2<br>4.3  |                                                                                                              | 48               |

|   | 4.0         |                                                                                                              | 49               |

|   |             |                                                                                                              | ±9<br>51         |

|   |             |                                                                                                              | 51               |

|   |             | •                                                                                                            | 51               |

|   |             | 4.3.4       Output Block                                                                                     |                  |

|   | 4.4         | -                                                                                                            | 56               |

|   | 4.4<br>4.5  |                                                                                                              | 66               |

|   | 4.5<br>4.6  |                                                                                                              | 67               |

|   | 4.0         |                                                                                                              | 67               |

|   |             |                                                                                                              | 68               |

|   |             | -                                                                                                            |                  |

|   | 17          |                                                                                                              | 70<br>75         |

|   | 4.7         | v                                                                                                            |                  |

|   |             |                                                                                                              | 75               |

|   |             | 4.7.2 Driver Performance with 50V voltage supply                                                             | 79               |

| <b>5</b> | Conclusions                                                     | 82 |

|----------|-----------------------------------------------------------------|----|

|          | 5.1 Future Work                                                 | 83 |

| 6        | Appendix A - Expected and Simulated Results from the new design | 84 |

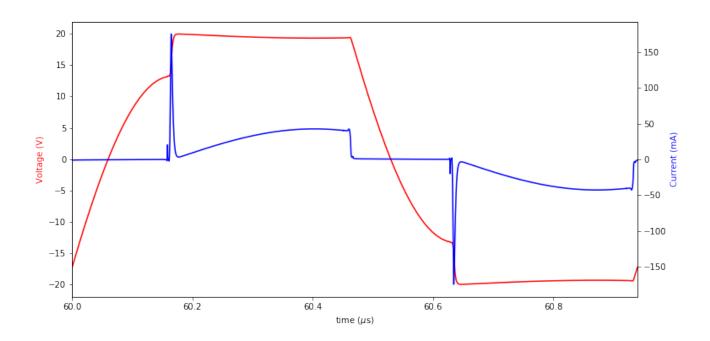

|          | 6.1 Output Waveform with 20V Supply                             | 84 |

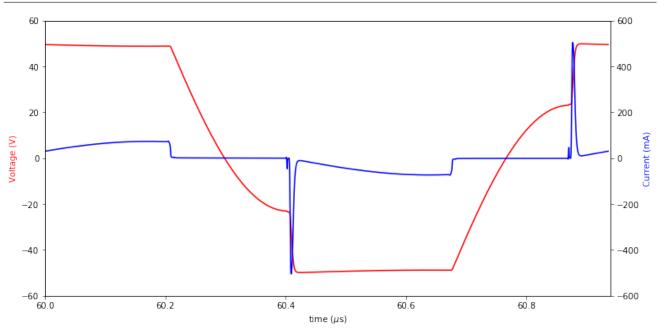

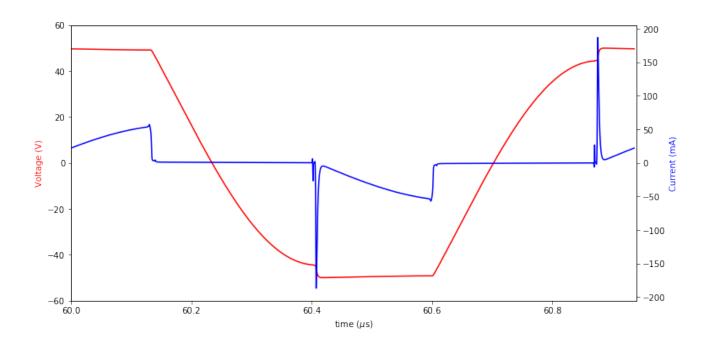

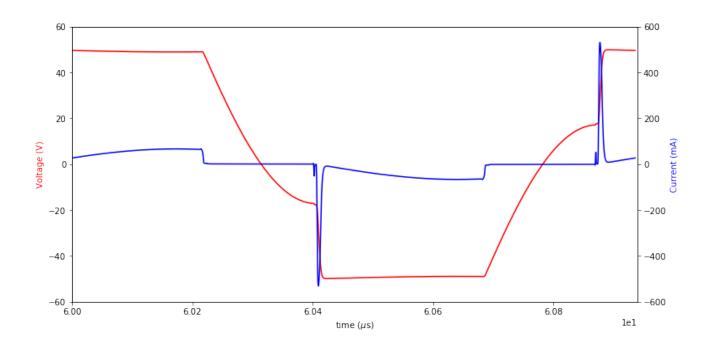

|          | 6.2 Output Waveform with 50V Supply                             | 88 |

| 7        | Appendix B - Parameters Extraction                              | 92 |

| 8        | Appendix C - MOSFET Capacitance                                 | 99 |

|          | 8.1 Gate Capacitance                                            | 99 |

|          | 8.2 MOSFET Drain Capacitance                                    | 99 |

# List of Figures

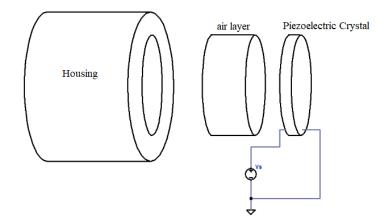

| 2.1  | Exploded view of a transducer $[3]$                                                        | 5  |

|------|--------------------------------------------------------------------------------------------|----|

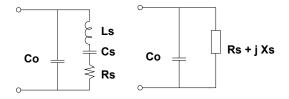

| 2.2  | Piezoelectric transducer simplified equivalent circuit.                                    | 5  |

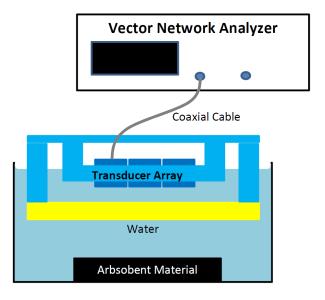

| 2.3  | Measuring the impedance of the transducers                                                 | 6  |

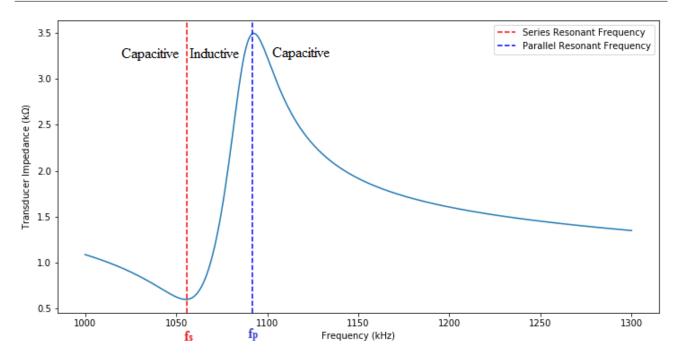

| 2.4  | Magnitude of the Transducer Impeadance vs Operating Frequency. $f_s$ is the series         |    |

|      | resonant frequency, where as $f_p$ is the parallel resonant frequency [15]                 | 7  |

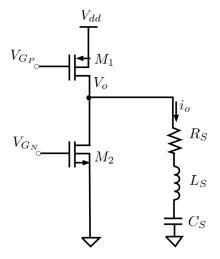

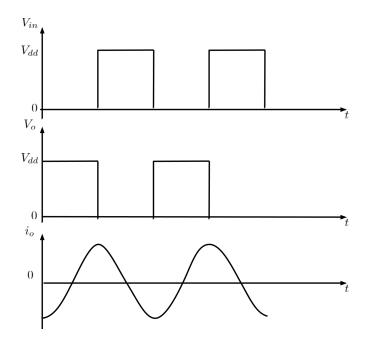

| 2.5  | Schematic of class D amplifier[14]                                                         | 9  |

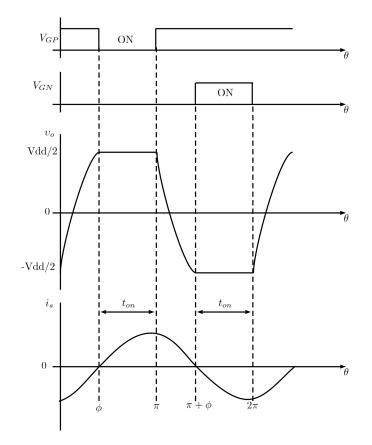

| 2.6  | Waveforms of class D amplifier [14]                                                        | 10 |

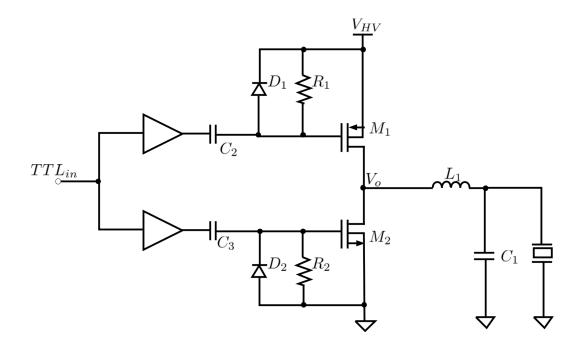

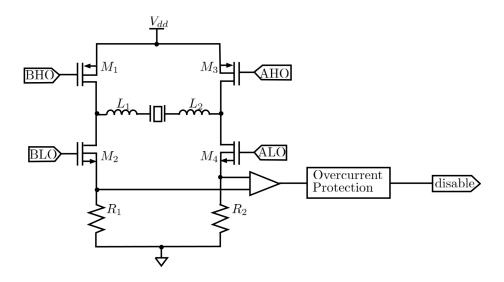

| 2.7  | Schematic of the transducer driver proposed by Hall and Cain                               | 10 |

| 2.8  | Schematic of class D Amplifier proposed by Agbossou [15]                                   | 11 |

| 2.9  | Schematic of a class D amplifier proposed by Yang and Xu [16]                              | 12 |

| 2.10 | Schematic of the switched-mode amplifier proposed by Lewis and Olbricht $\left[ 21\right]$ | 12 |

| 2.11 | Schematic of LIPUS amplifier proposed in [22]                                              | 13 |

| 2.12 | Proposed Amplifier from O. Farhanieh [20]                                                  | 14 |

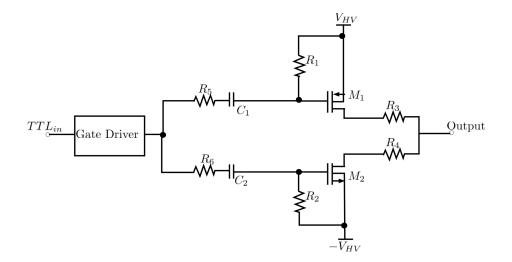

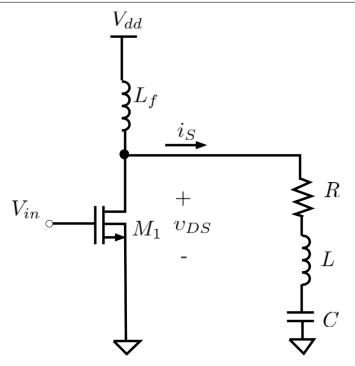

| 2.13 | Schematic of class E amplifier [14]                                                        | 15 |

| 2.14 | Waveforms of class E amplifier $[14]$                                                      | 16 |

| 2.15 | Yuan's class E Amplifier Design [10]                                                       | 16 |

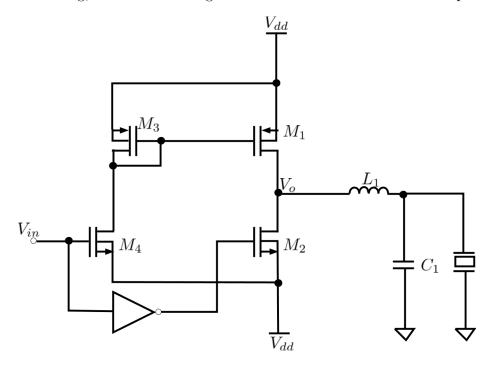

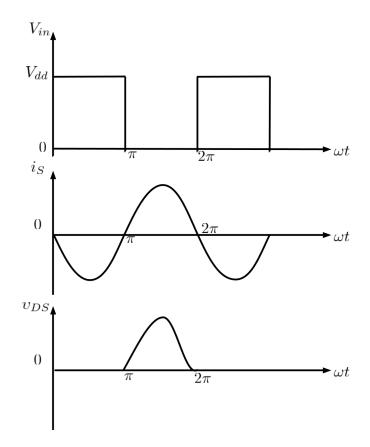

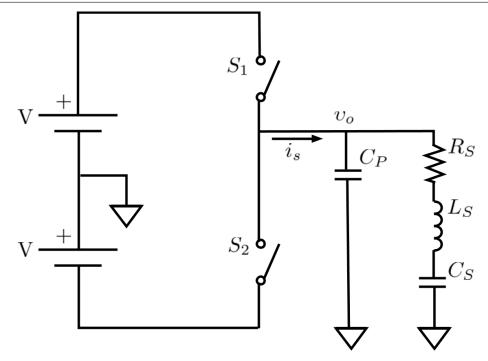

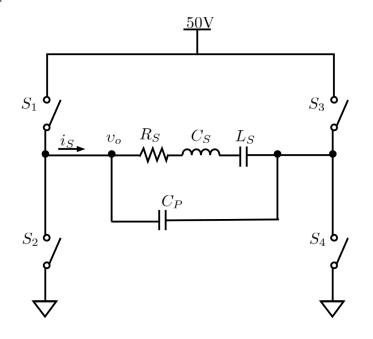

| 2.16 | Class DE simplified circuit                                                                | 17 |

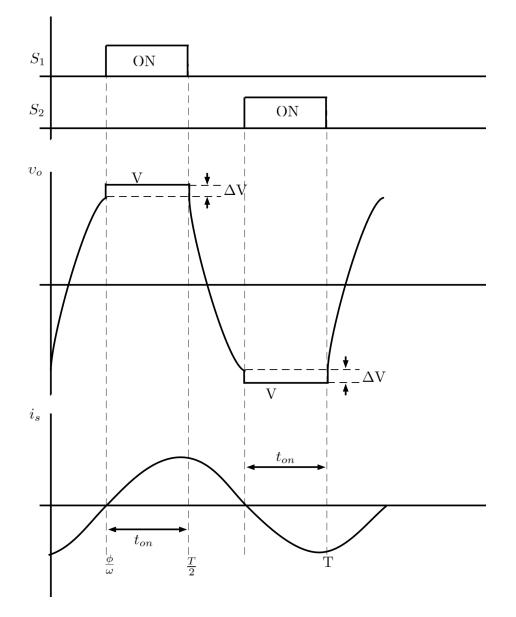

| 2.17 | Class DE waveform                                                                          | 18 |

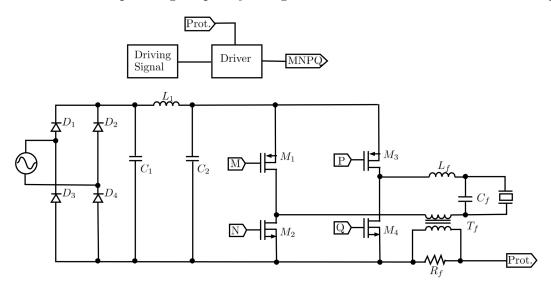

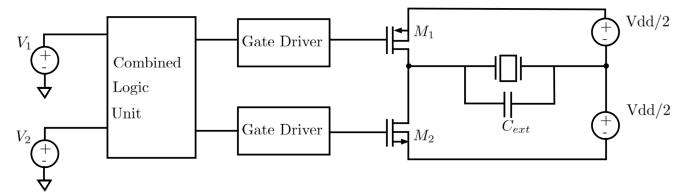

| 2.18 | Overall system of Wai's design $[3]$                                                       | 20 |

| 2.19 | Proposed design by Ruiqi [4]                                                               | 20 |

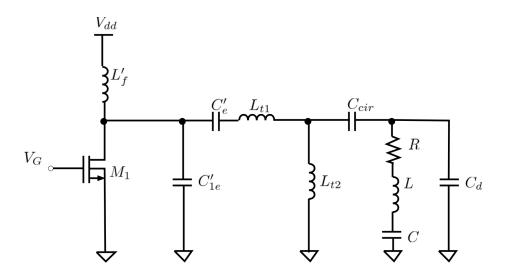

| 3.1  | Simplified class DE circuit                                                                | 24 |

| 3.2  | Class DE output waveform outside optimum condition                                         | 25 |

| 3.3  | Transducer array used in this work                                                                                                  | 29       |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

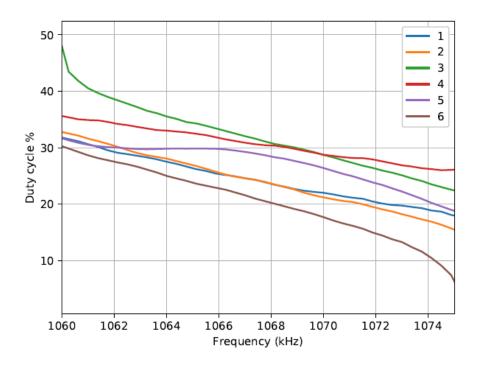

| 3.4  | Optimum duty cycle vs frequency for the transducer array                                                                            | 31       |

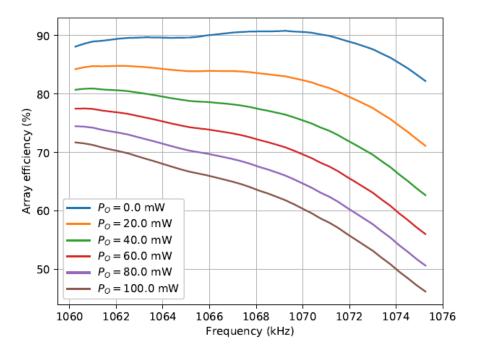

| 3.5  | Power efficiency vs frequency for the transducer array with different driving power                                                 |          |

|      | losses                                                                                                                              | 32       |

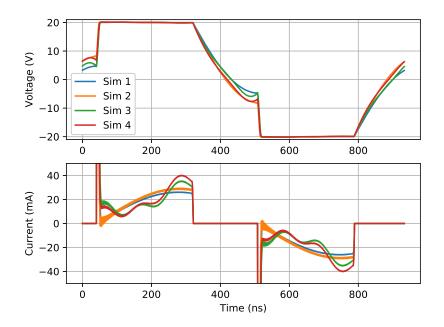

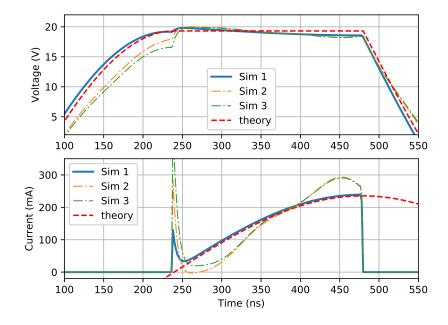

| 3.6  | Trans 3 output voltage and current                                                                                                  | 33       |

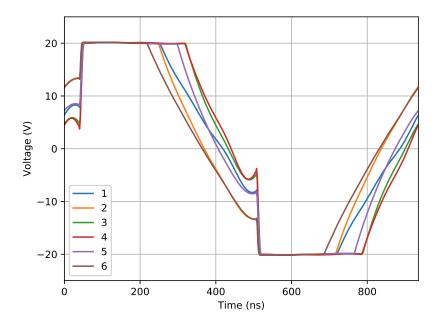

| 3.7  | Sim 3 Output voltages                                                                                                               | 34       |

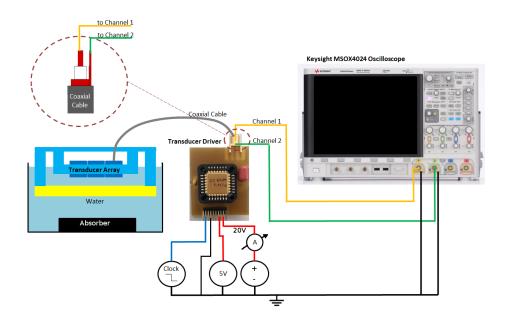

| 3.8  | Experimental Setup                                                                                                                  | 35       |

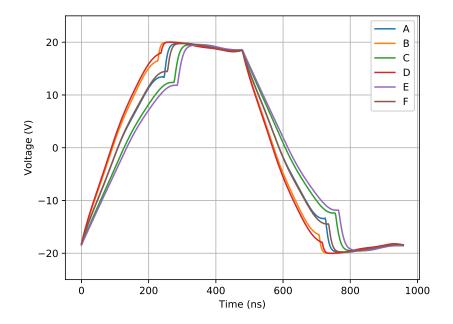

| 3.9  | Experimental output voltage for all transducers                                                                                     | 35       |

| 3.10 | Real-life image of the transducer array used in this work                                                                           | 37       |

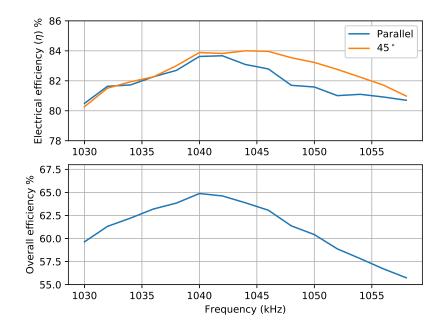

| 3.11 | Transducer conversion efficiency as a function of frequency                                                                         | 39       |

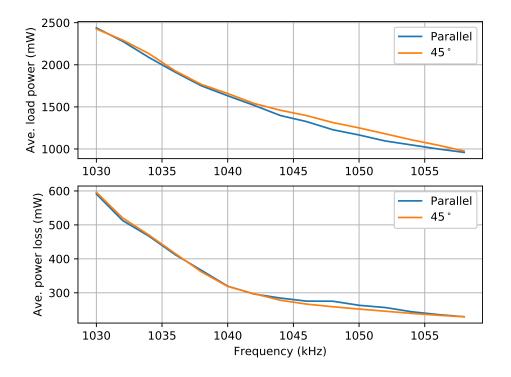

| 3.12 | Electrical load power and losses vs. frequency                                                                                      | 41       |

| 3.13 | Array electrical efficiency $(\eta)$ and overall combined electrical-acoustic efficiency                                            |          |

|      | vs. frequency.                                                                                                                      | 42       |

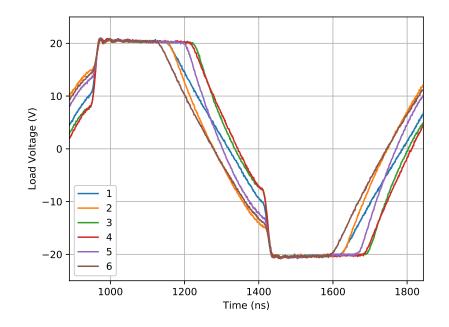

| 3.14 | Output voltage for all transducers using the accurate transducer model (Sim 2). $% \left( \left( {{\rm{Sim}}\;2} \right) \right)$ . | 44       |

| 3.15 | Output voltage and current waveforms for Transducer D                                                                               | 45       |

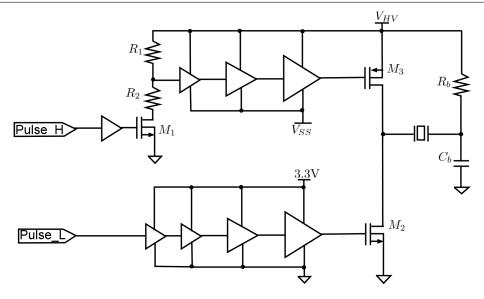

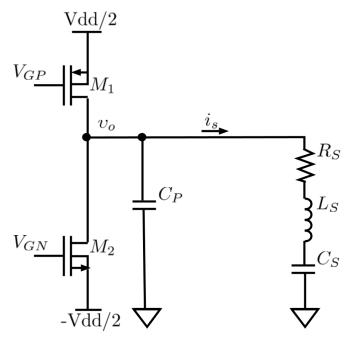

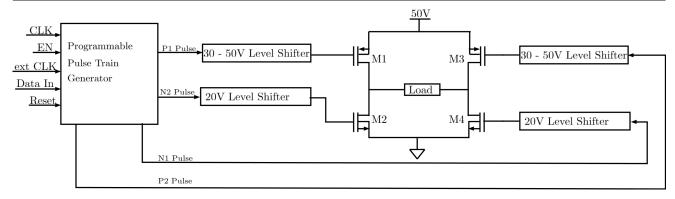

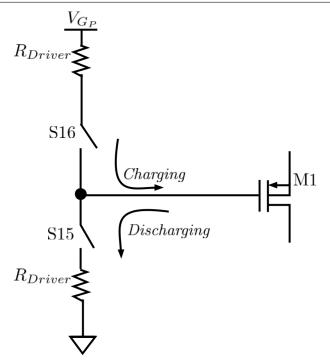

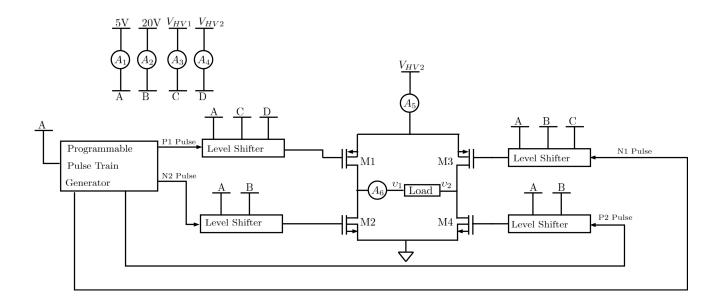

| 4.1  | Proposed transducer driver                                                                                                          | 48       |

| 4.2  |                                                                                                                                     | 49       |

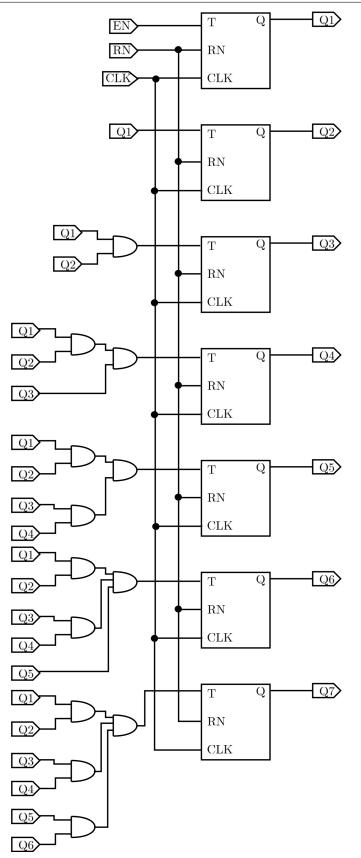

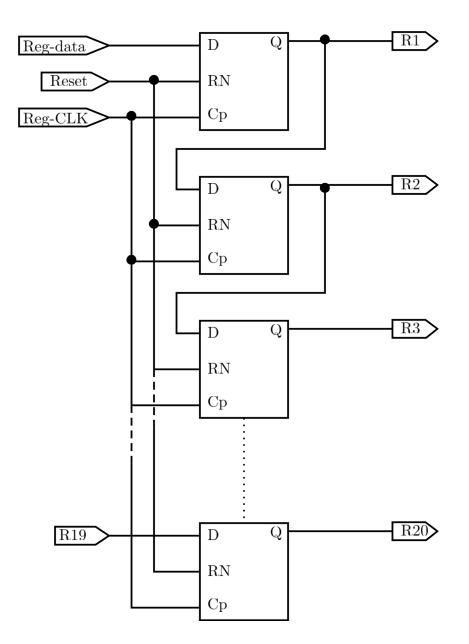

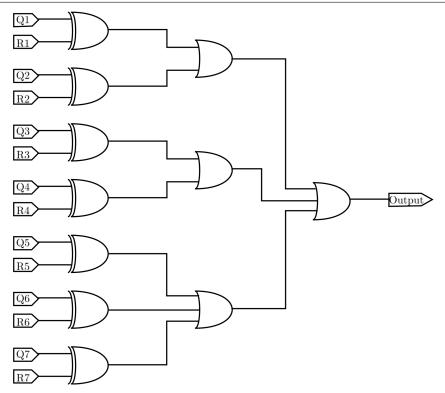

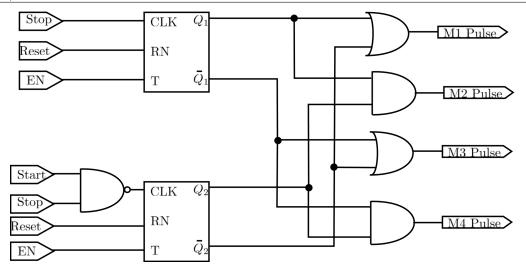

| 4.3  |                                                                                                                                     | 50       |

| 4.4  |                                                                                                                                     | 52       |

| 4.5  |                                                                                                                                     | 53       |

| 4.6  |                                                                                                                                     | 54       |

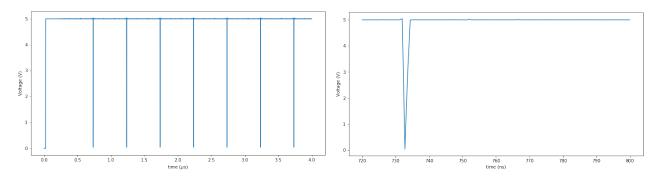

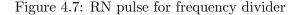

| 4.7  |                                                                                                                                     | 54       |

| 4.8  | Zoomed view of RN pulse                                                                                                             | 54       |

| 4.9  |                                                                                                                                     | 55       |

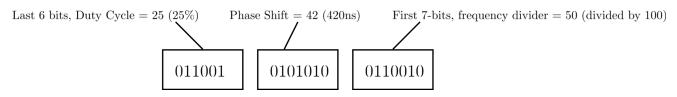

| 4.10 | Simulation results for programming the DLU system                                                                                   | 56       |

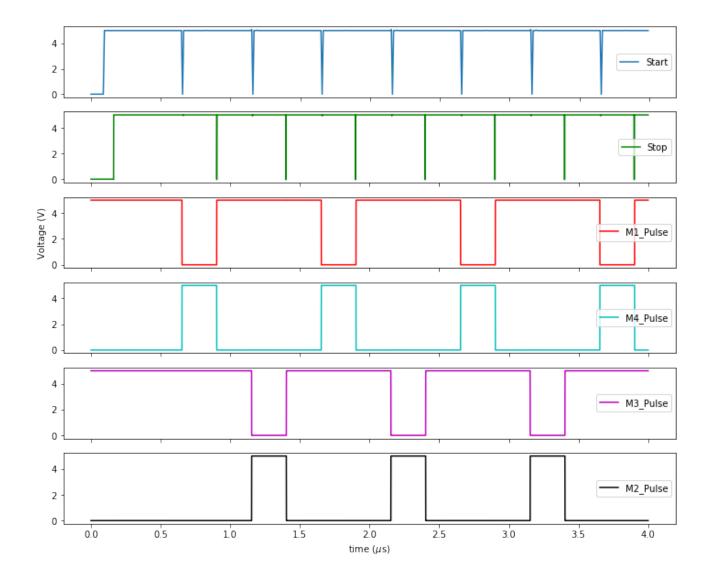

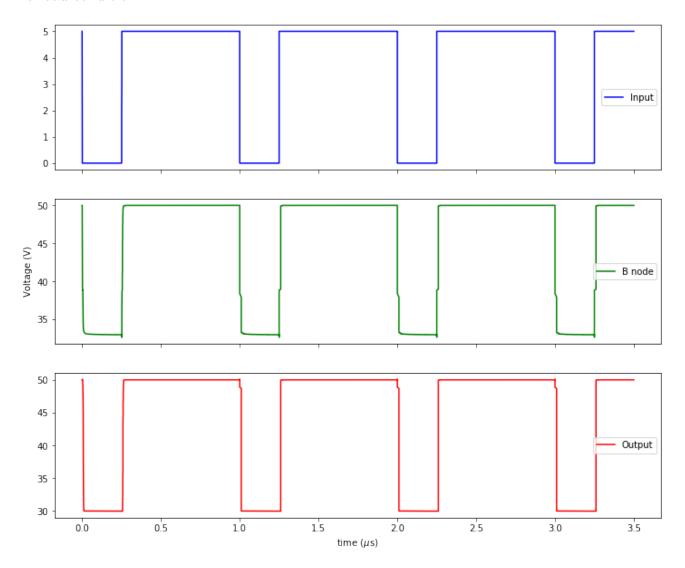

| 4.11 | Outputs of the Pulse Train Generator                                                                                                | 57       |

| 4.12 | Schematic of a conventional level shifter                                                                                           | 58       |

|      |                                                                                                                                     | 50       |

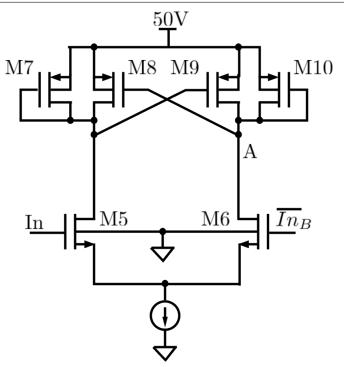

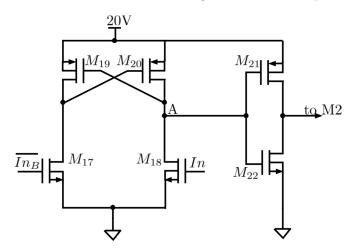

|      | Level Shifter used in $[3]$ and $[4]$                                                                                               | 59       |

| 4.14 |                                                                                                                                     | 59<br>60 |

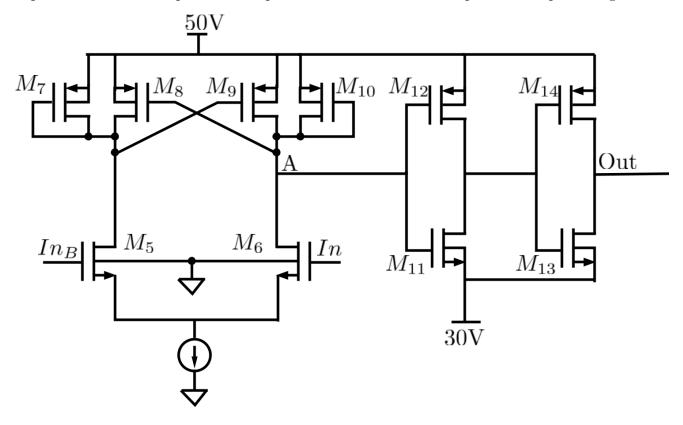

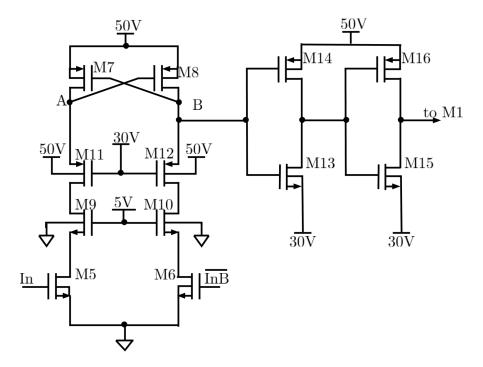

|      | Schematic diagram for the 30-50 V level shifter                                                                                     |          |

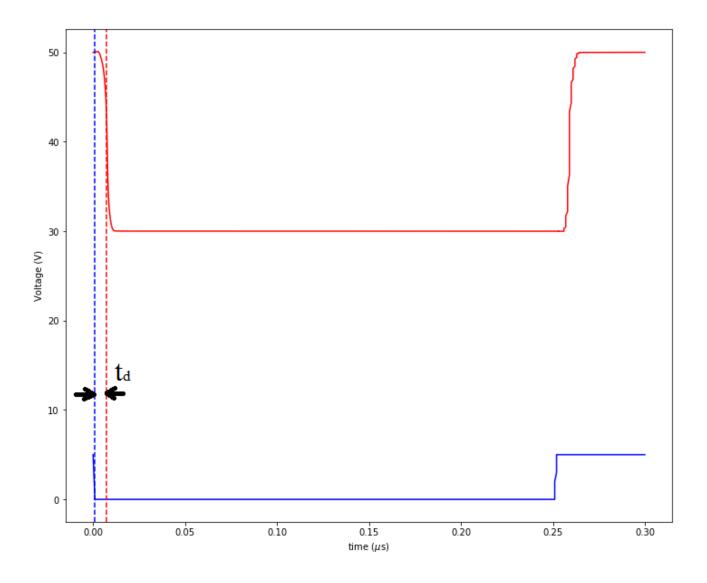

| 4.16 | Simulated results of the proposed Level Shifter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.17 | Close up view of the level shifter output waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

| 4.18 | 20V Level Shifter design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

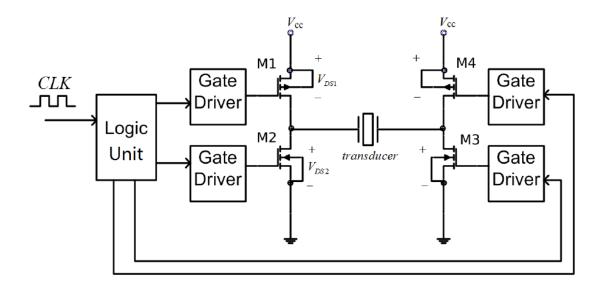

| 4.19 | Simplified class DE amplifier in full bridge configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67 |

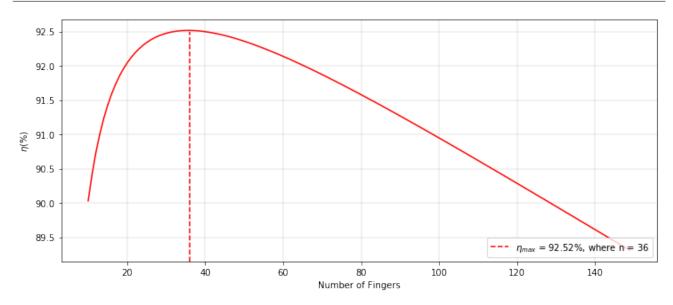

| 4.20 | Power efficiency vs number of fingers for transducer array used in section 3.3 $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71 |

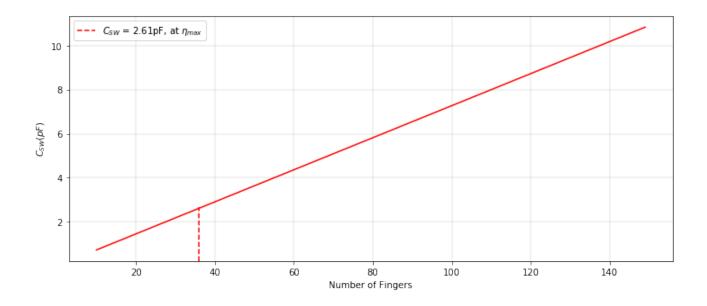

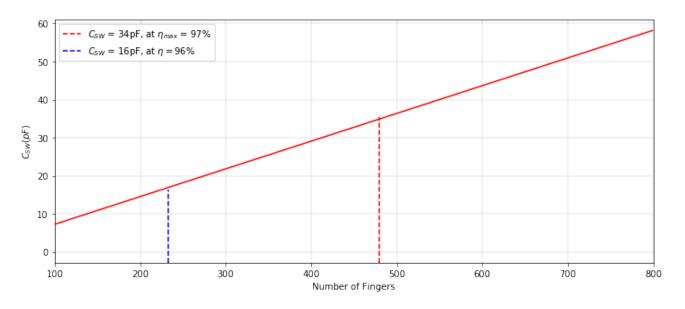

| 4.21 | Switch capacitance vs number of fingers for transducer array used in section $3.3$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72 |

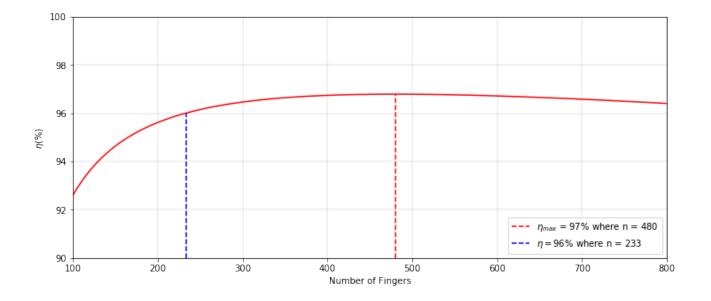

| 4.22 | Power efficiency vs number of fingers for transducer array used in section 3.3 $\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

| 4.23 | Switch capacitance vs number of fingers for transducer array used in section $3.4$ $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73 |

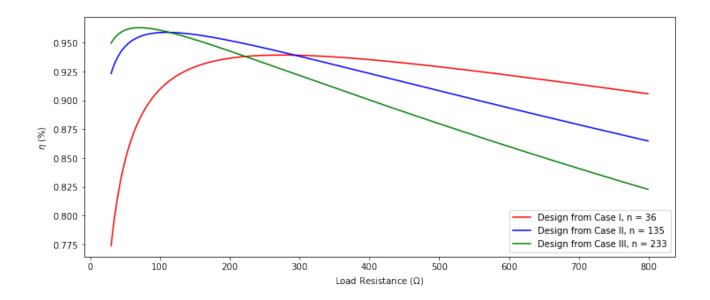

| 4.24 | Power efficiency vs load resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74 |

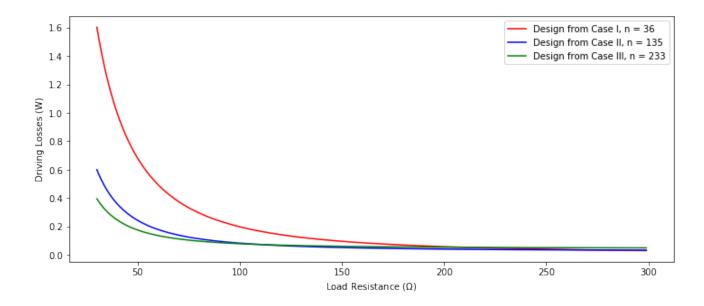

| 4.25 | Power losses from all 3 cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

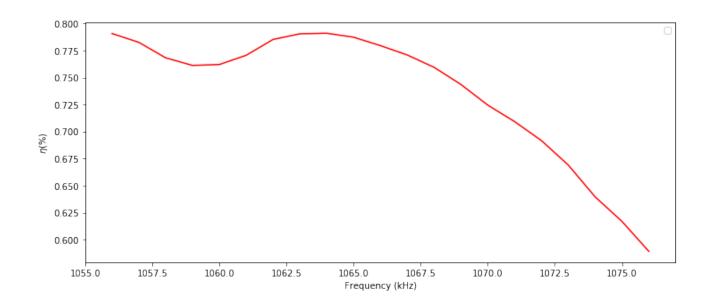

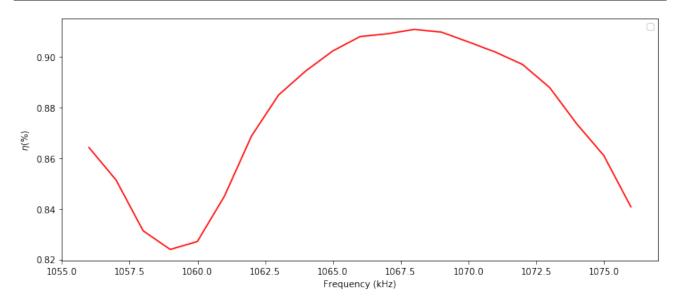

| 4.26 | $\eta$ vs. frequency when the power supply is connected to 20 V $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77 |

| 4.27 | Simulation setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77 |

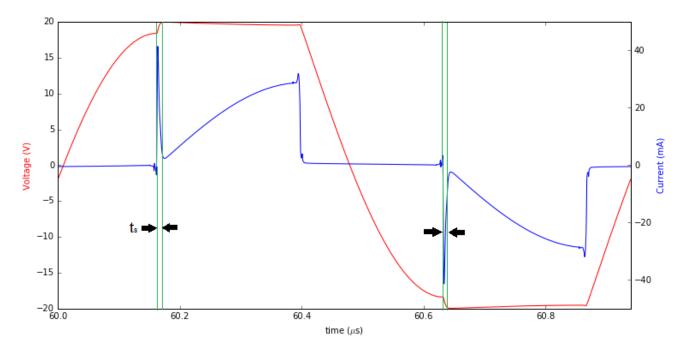

| 4.28 | Extracting switching loss from simulation, red line is $v_o$ , and blue line is $i_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78 |

| 4.29 | $\eta$ vs. frequency when using 50 V voltage supply $\hdots \hdots $ | 80 |

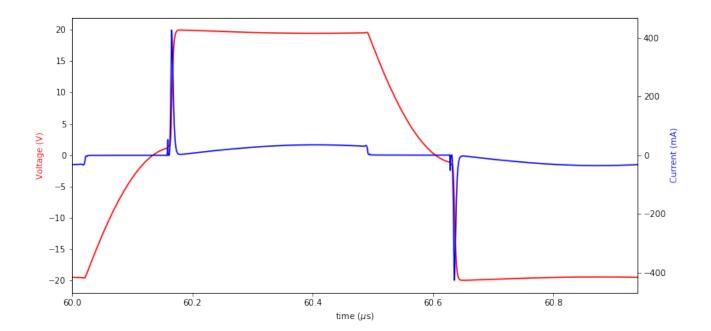

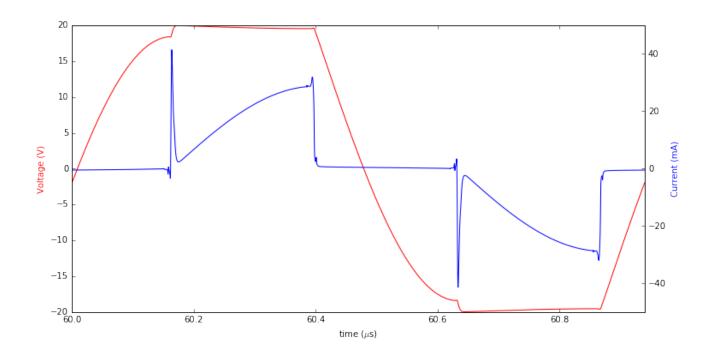

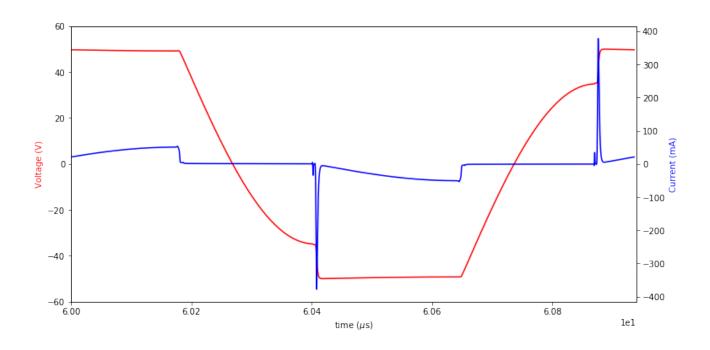

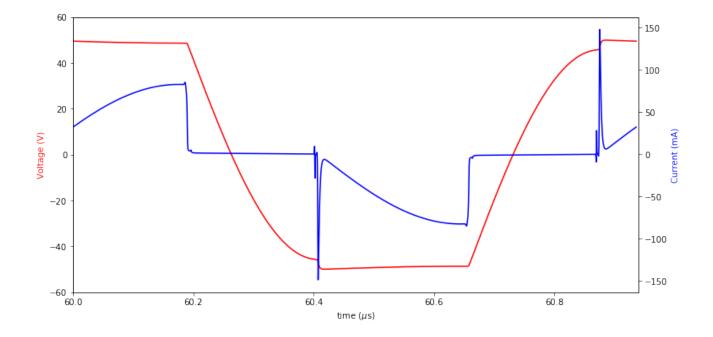

| 6.1  | Output Voltage and Current of transducer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85 |

| 6.2  | Output Voltage and Current of transducer 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85 |

| 6.3  | Output Voltage and Current of transducer 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

| 6.4  | Output Voltage and Current of transducer 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

| 6.5  | Output Voltage and Current of transducer 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87 |

| 6.6  | Output Voltage and Current of transducer 6 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |

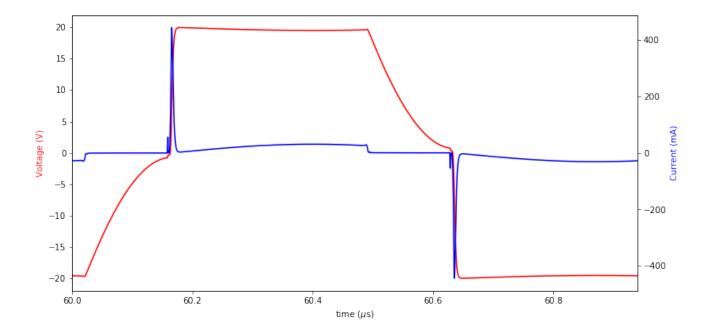

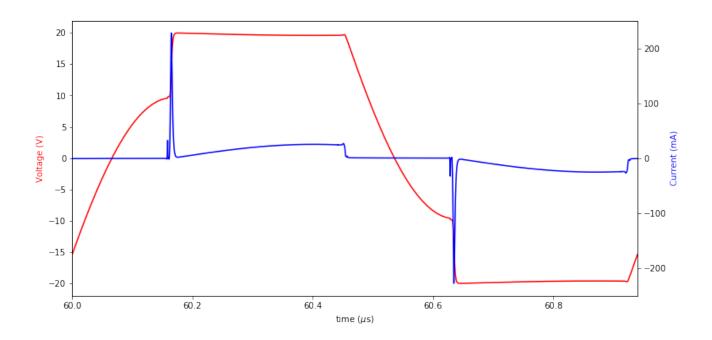

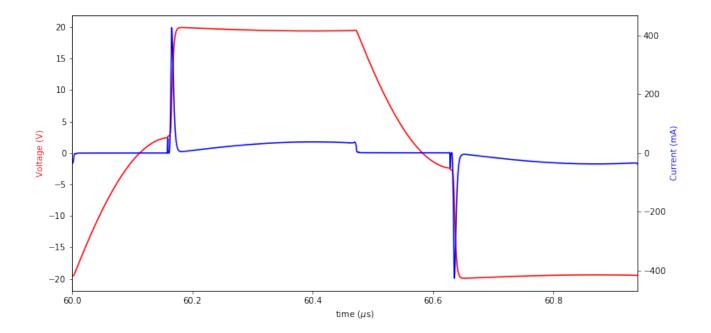

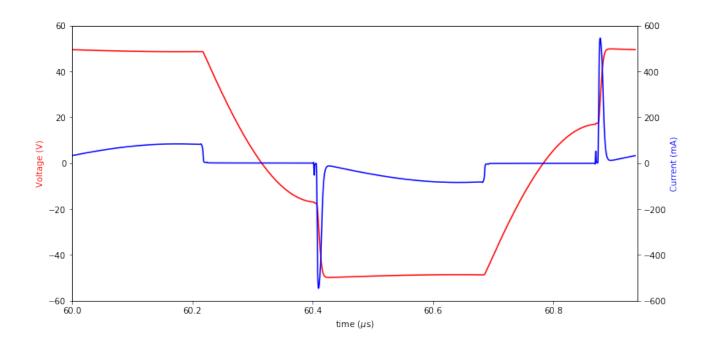

| 6.7  | Output Voltage and Current of transducer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88 |

| 6.8  | Output Voltage and Current of transducer 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 |

| 6.9  | Output Voltage and Current of transducer 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 |

| 6.10 | Output Voltage and Current of transducer 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

| 6.11 | Output Voltage and Current of transducer 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

| 6.12 | Output Voltage and Current of transducer 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91 |

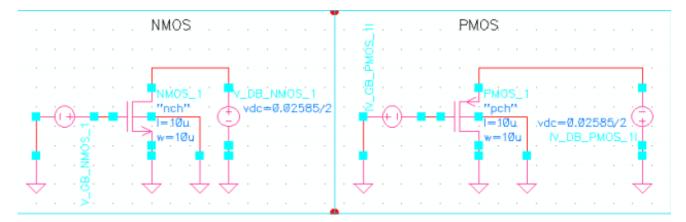

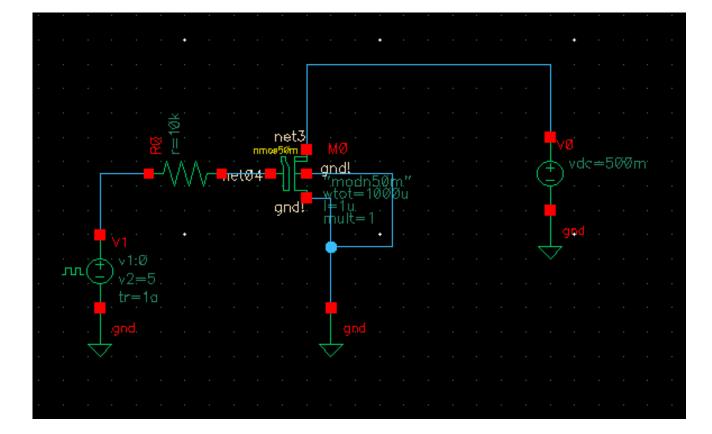

| 7.1  | $I_{SQ}$ and $V_t$ extraction circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92 |

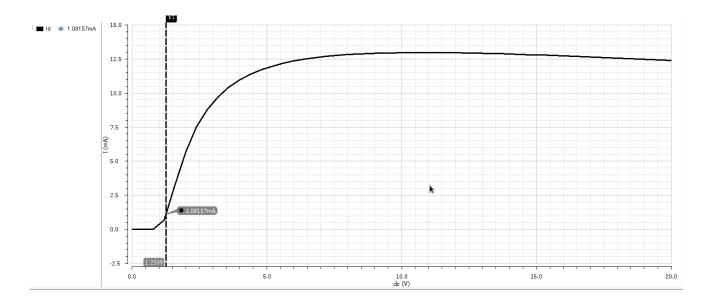

| 7.2  | $I_D vsV_{GB}$ for NMOS50M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93 |

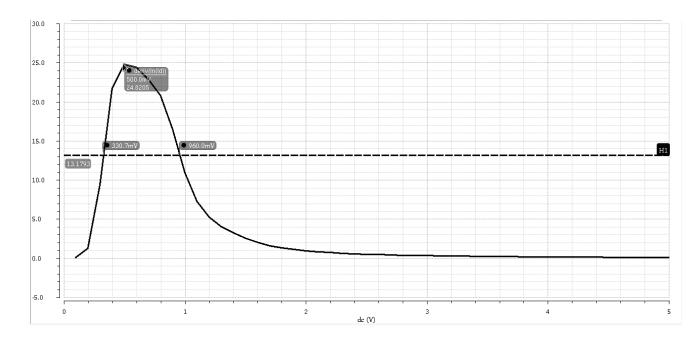

| 7.3  | Obtaining $V_t$ for NMOS50M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93 |

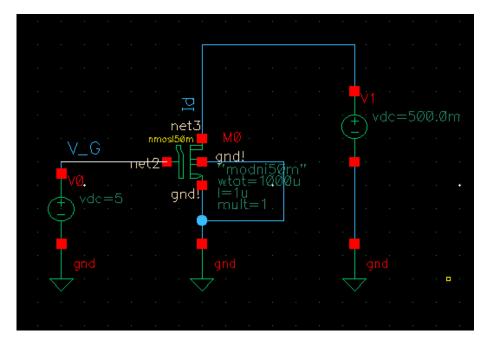

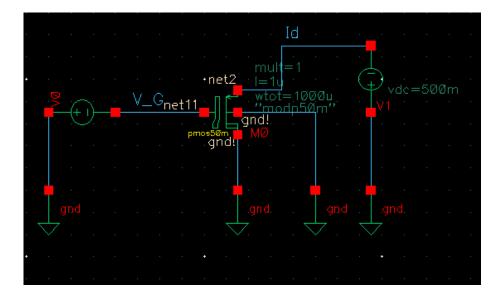

| 7.4 | Circuit setup to extract parameters for NMOS50M                                     | 94  |

|-----|-------------------------------------------------------------------------------------|-----|

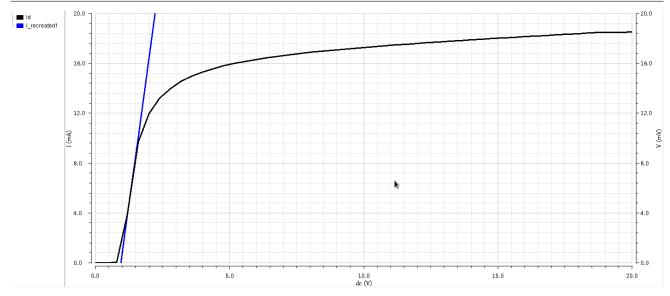

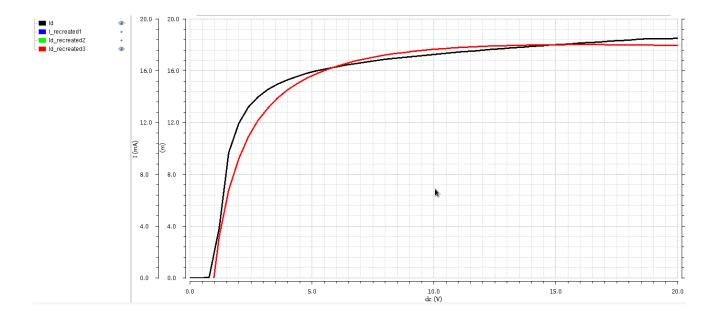

| 7.5 | measure $I_D$ (black) and recreated $I_D$ (blue) with only K parameter for NMOS50M  | 95  |

| 7.6 | Recreated $I_D$ using the extracted parameters (red) and the measure $I_D$ (black)  | 96  |

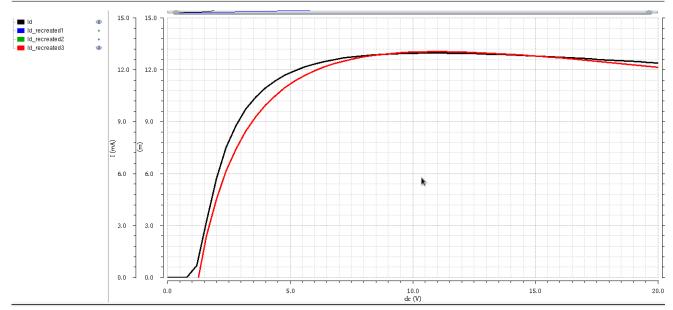

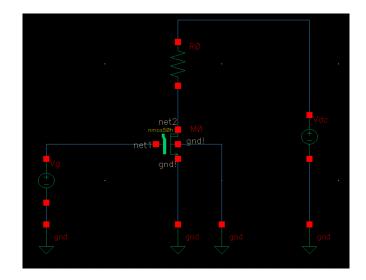

| 7.7 | Circuit setup to extract parameters for PMOS50M                                     | 96  |

| 7.8 | Recreated $I_D$ for PMOS using the extracted parameters (red) and the measure $I_D$ |     |

|     | $(black) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                    | 97  |

| 7.9 | Simulation setup to extract the actual MOSFET on-resistance                         | 98  |

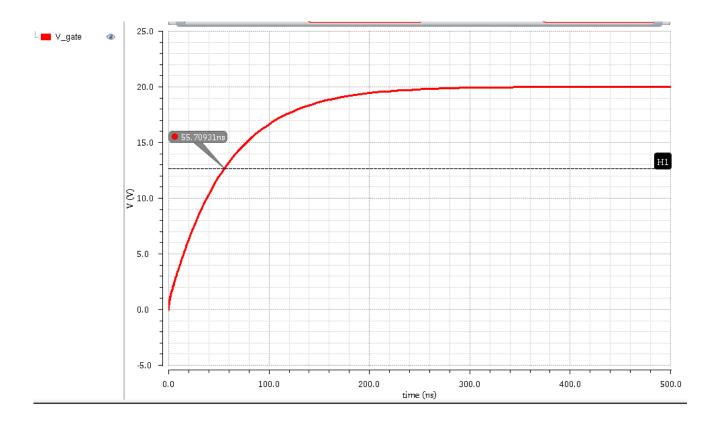

| 8.1 | Circuit setup to find the gate capacitance                                          | 100 |

| 8.2 | Gate capacitance charging curve                                                     | 101 |

# List of Tables